Maxim Integrated DS33Z41 User Manual

Page 35

DS33Z41 Quad IMUX Ethernet Mapper

35 of 167

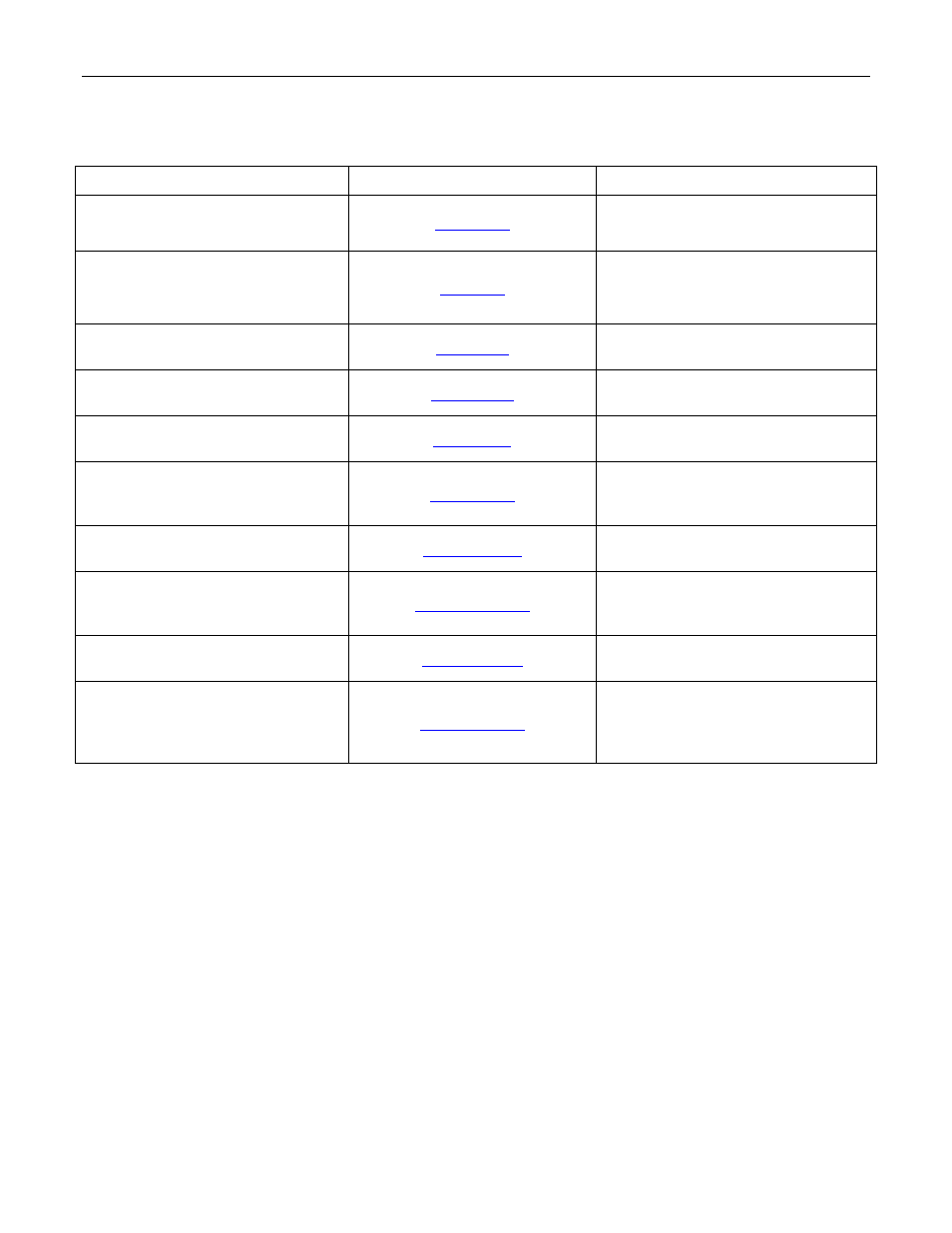

The command and status registers for the IMUX function are detailed below:

Table 8-4. Command and Status for the IMUX for Processor Communication

REGISTER NAME COMMENTS

IMUX Configuration Register

GL.IMXCN

Used to configure the number of links

participating and select T1 or E1.

IMUX Command Register

GL.IMXC

Used to issue commands for link

management

IMUX Sync Status Register

GL.IMXSS

Provides the real time sync status of

the 4 transmit and receive links

IMUX Sync Latched Status Register

GL.IMXSLS

Latched status register for the IMXSS

register.

IMUX Interrupt Mask Register

GL.IMXSIE

Interrupt enable bits for Sync Latched

Status bits

Differential Delay Register

GL.IMXDFD

Provides the largest differential delay

value for the receive path. Measured

only at link initialization.

Differential Delay Error Interrupt

Enable Register

GL.IMXDFEIE

Interrupt enable for the differential

delay register.

Differential Delay Latched Status

Register

GL.IMXDFDELS

Latched Status for GL.IMXDFD. Note

that differential delay is measured

only at link initiation.

OOF Interrupt Enable

GL.IMXOOFIE

Interrupt enable for the IMXOOFLS

register.

OOF Latched Status Register

GL.IMXOOFLS

Indicates out of frame conditions for

both ends of the communication. If

detected, the user must re-initiate all

links.