Maxim Integrated DS33Z41 User Manual

Page 122

DS33Z41 Quad IMUX Ethernet Mapper

122 of 167

Register Name:

SU.QRIE

Register Description:

Receive Queue Cross Threshold Enable

Register Address:

15Ch

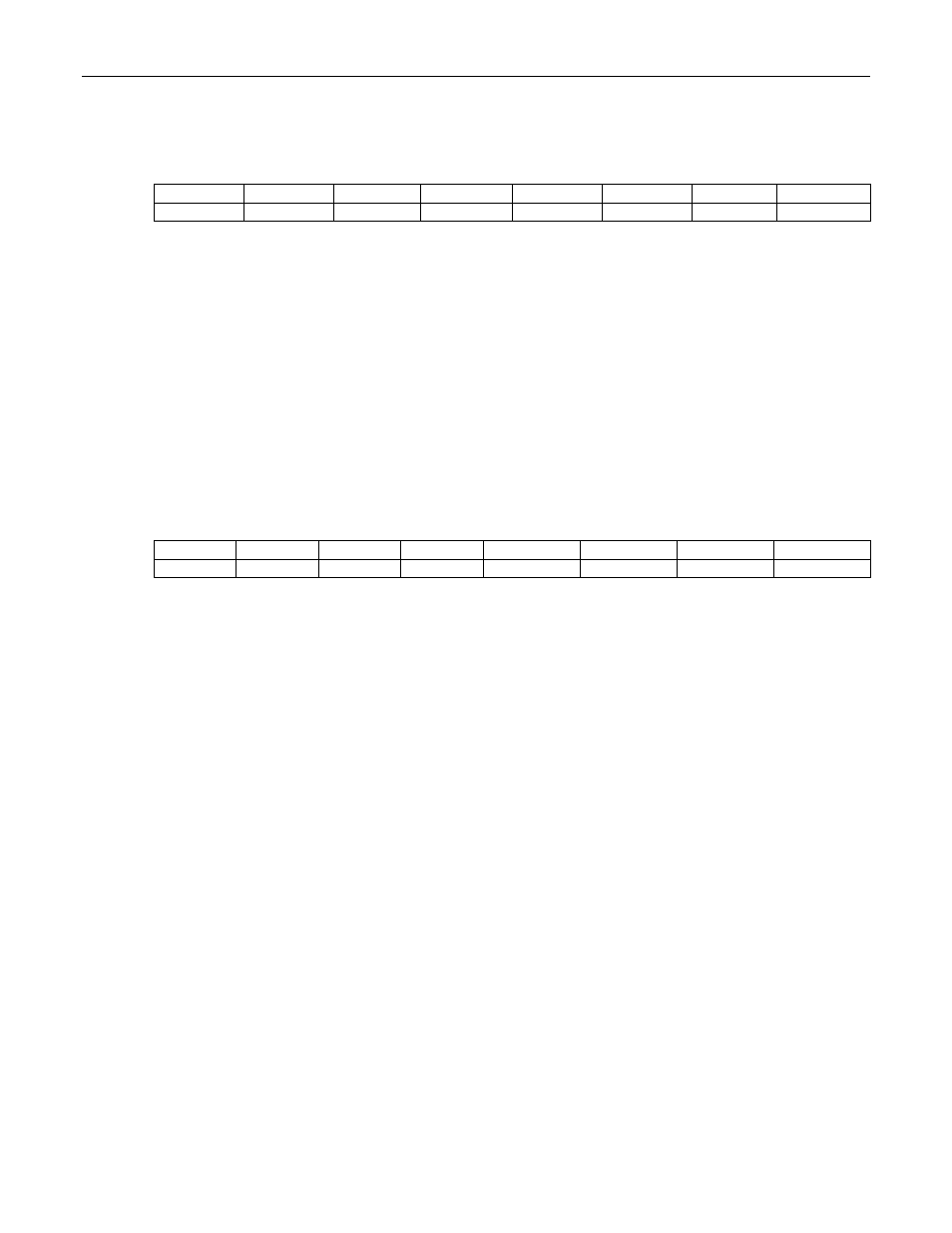

Bit

# 7 6 5 4 3 2 1 0

Name — — — —

RFOVFIE

RQVFIE

RQLTIE

RQHTIE

Default

0 0 0 0 0 0 0 0

Bit 3: Receive FIFO Overflow Interrupt Enable (RFOVFIE). If this bit is set, the interrupt is enabled for

RFOVFLS.

Bit 2: Receive Queue Overflow Interrupt Enable (RQVFIE). If this bit is set, the interrupt is enabled for

RQOVFLS.

Bit 1: Receive Queue Crosses Low Threshold Interrupt Enable (RQLTIE). If this bit is set, the watermark

interrupt is enabled for RQLTS.

Bit 0: Receive Queue Crosses High Threshold Interrupt Enable (RQHTIE). If this bit is set, the watermark

interrupt is enabled for RQHTS.

Register Name:

SU.QCRLS

Register Description:

Queue Cross Threshold Latched Status

Register Address:

15Dh

Bit

#

7

6

5

4 3 2 1 0

Name — — — —

RFOVFLS

RQOVFLS

RQHTLS

RQLTLS

Default

—

—

—

— — — — —

Bit 3: Receive FIFO Overflow latched Status (RFOVFLS). This bit is set if the receive FIFO overflows for the

data to be transmitted from the MAC to the SDRAM.

Bit 2: Receive Queue Overflow Latched Status (RQOVFLS). This bit is set if the receive queue has

overflowed. This register is cleared after a read.

Bit 1: Receive Queue for Connection Crossed High Threshold Latched Status (RQHTLS). This bit is set if

the receive queue crosses the high watermark. This register is cleared after a read.

Bit 0: Receive Queue for Connection Crossed Low Threshold Latched Status (RQLTLS). This bit is set if the

receive queue crosses the low watermark. This register is cleared after a read.

Note the bit order differences in the high/low threshold indications in SU.QCRLS and the interrupt enables in

SU.QRIE.