Maxim Integrated DS33Z41 User Manual

Page 95

DS33Z41 Quad IMUX Ethernet Mapper

95 of 167

Register Name:

LI.TBCR0

Register Description:

Transmit Byte Count Byte 0

Register Address:

0D0h

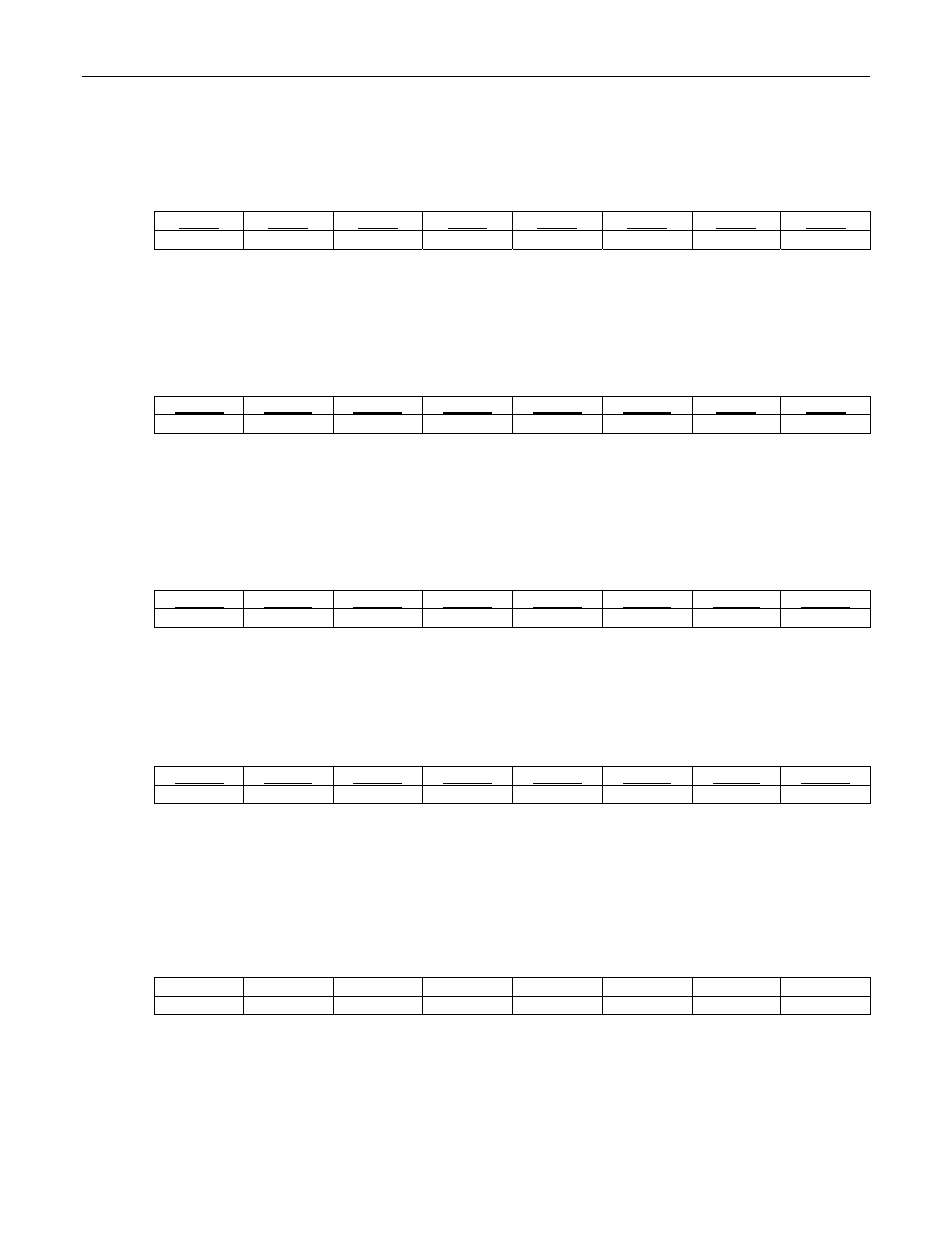

Bit

# 7 6 5 4 3 2 1 0

Name TBC7 TBC6 TBC5 TBC4 TBC3 TBC2 TBC1 TBC0

Default

0 0 0 0 0 0 0 0

Bits 7 to 0: Transmit Byte Count (TBC7 to TBC0). Eight bits of 32-bit value. Register description below.

Register Name:

LI.TBCR1

Register Description:

Transmit Byte Count Byte 1

Register Address:

0D1h

Bit

# 7 6 5 4 3 2 1 0

Name TBC15 TBC14 TBC13 TBC12 TBC11 TBC10 TBC9 TBC8

Default

0 0 0 0 0 0 0 0

Bits 7 to 0: Transmit Byte Count (TBC15 to TBC8). Eight bits of 32-bit value. Register description below.

Register Name:

LI.TBCR2

Register Description:

Transmit Byte Count Byte 2

Register Address:

0D2h

Bit

# 7 6 5 4 3 2 1 0

Name TBC23 TBC22 TBC21 TBC20 TBC19 TBC18 TBC17 TBC16

Default

0 0 0 0 0 0 0 0

Bits 7 to 0: Transmit Byte Count (TBC23:TBC16). Eight bits of 32-bit value. Register description below.

Register Name:

LI.TBCR3

Register Description:

Transmit Byte Count Byte 3

Register Address:

0D3h

Bit

# 7 6 5 4 3 2 1 0

Name TBC31 TBC30 TBC29 TBC28 TBC27 TBC26 TBC25 TBC24

Default

0 0 0 0 0 0 0 0

Bits 7 to 0: Transmit Byte Count (TBC31 to TBC24). These 32 bits indicate the number of packet bytes

inserted in the outgoing data stream.

Register Name:

LI.TMEI

Register Description:

Transmit Manual Error Insertion

Register Address:

0D4h

Bit

# 7 6 5 4 3 2 1 0

Name — — — — — — —

TMEI

Default

0 0 0 0 0 0 0 0

Bit 0: Transmit Manual Error Insertion (TMEI). A zero to one transition will insert a single error in the transmit

direction.