Ethernet interface registers, Ethernet interface register bit descriptions, Thernet – Maxim Integrated DS33Z41 User Manual

Page 112: Nterface, Egisters

DS33Z41 Quad IMUX Ethernet Mapper

112 of 167

9.6 Ethernet Interface Registers

The Ethernet Interface registers are used to configure RMII/MII bus operation and establish the MAC parameters

as required by the user. The MAC Registers cannot be addressed directly from the Processor port. The registers

below are used to perform indirect read or write operations to the MAC registers. The MAC Status Registers are

shown in

Table 9-7

. Accessing the MAC Registers is described in the Section

8.14

.

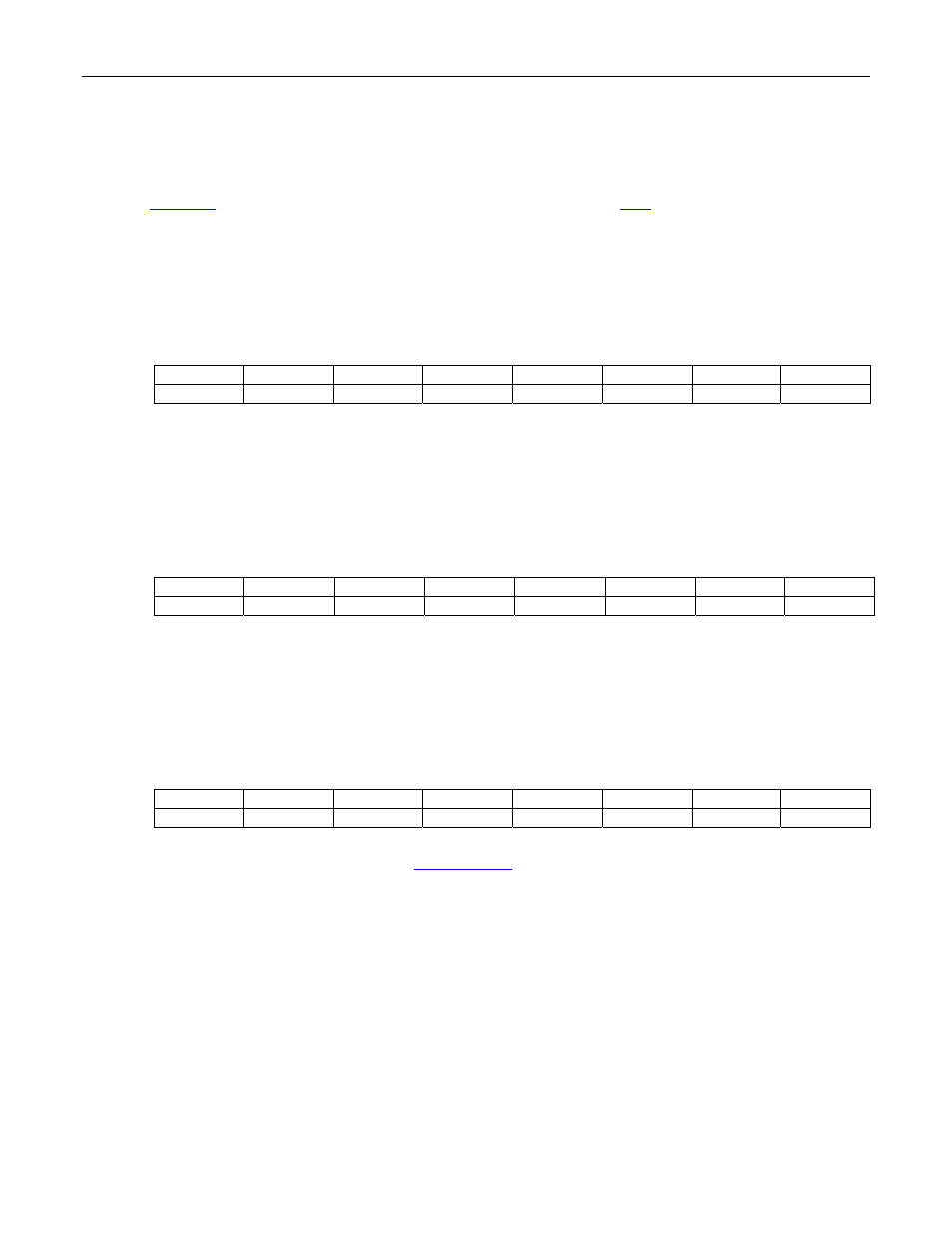

9.6.1 Ethernet Interface Register Bit Descriptions

Register Name:

SU.MACRADL

Register Description:

MAC Read Address Low Register

Register Address:

140h

Bit

# 7 6 5 4 3 2 1 0

Name MACRA7 MACRA6

MACRA5 MACRA4 MACRA3 MACRA2

MACRA1 MACRA0

Default

0 0 0 0 0 0 0 0

Bits 7 to 0: MAC Read Address (MACRA7 to MACRA0). Low byte of the MAC address. Used only for read

operations.

Register Name:

SU.MACRADH

Register Description:

MAC Read Address High Register

Register Address:

141h

Bit

# 7 6 5 4 3 2 1 0

Name

MACRA15

MACRA14

MACRA13

MACRA12

MACRA11

MACRA10

MACRA9

MACRA8

Default

0 0 0 0 0 0 0 0

Bits 7 to 0: MAC Read Address (MACRA15 to MACRA8). High byte of the MAC address. Used only for read

operations.

Register Name:

SU.MACRD0

Register Description:

MAC Read Data Byte 0

Register Address:

142h

Bit

# 7 6 5 4 3 2 1 0

Name MACRD7 MACRD6 MACRD5 MACRD4 MACRD3 MACRD2 MACRD1 MACRD0

Default

0 0 0 0 0 0 0 0

Bits 7 to 0: MAC Read Data Byte 0 (MACRD7 to MACRD0). One of four bytes of data read from the MAC. Valid

after a read command has been issued and the

SU.MACRWC

.MCS bit is zero.