Maxim Integrated DS33Z41 User Manual

Page 102

DS33Z41 Quad IMUX Ethernet Mapper

102 of 167

Register Name:

LI.RPPSRIE

Register Description:

Receive Packet Processor Status Register Interrupt Enable

Register Address:

106h

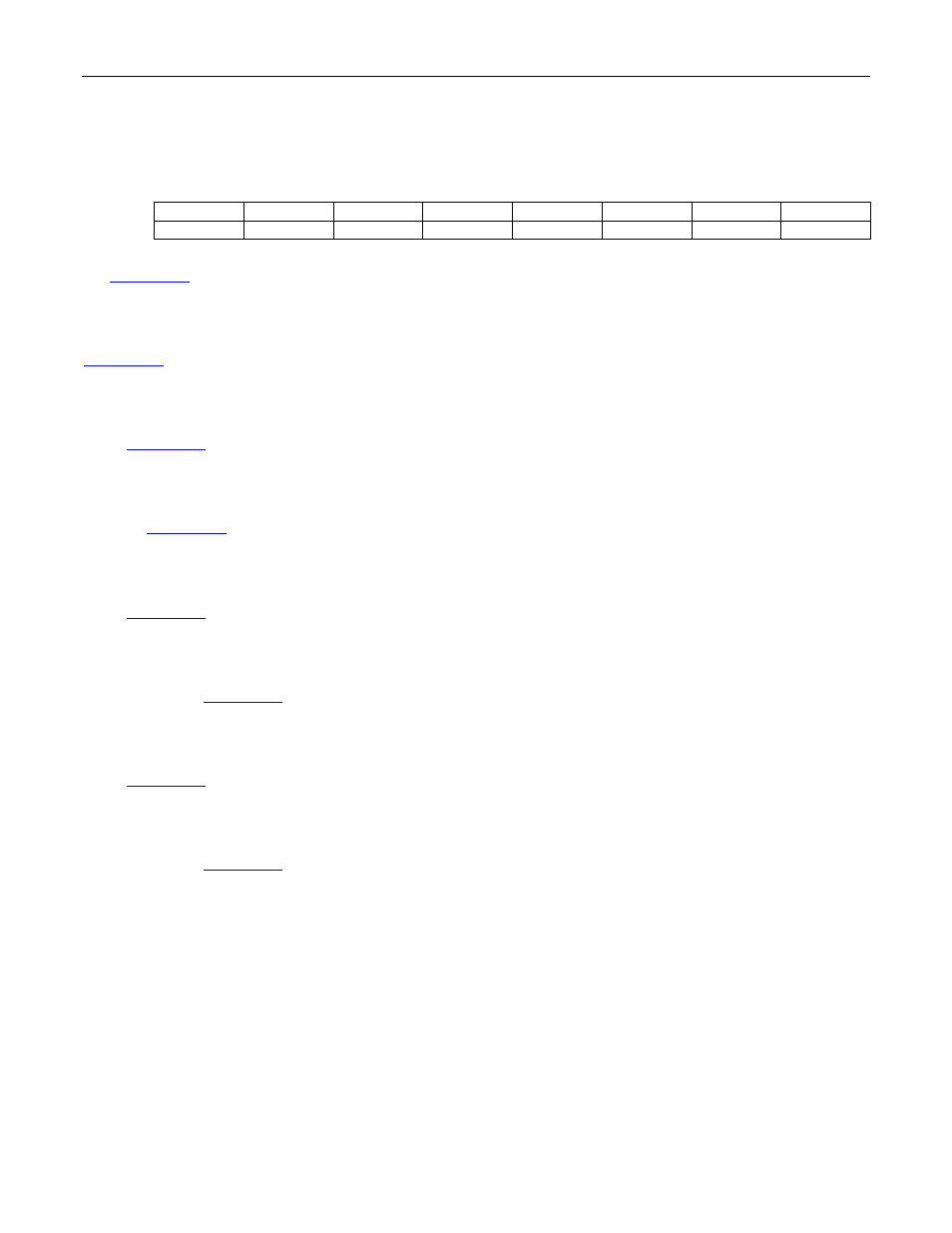

Bit

# 7 6 5 4 3 2 1 0

Name REPIE RAPIE

RIPDIE

RSPDIE

RLPDIE REPCIE RAPCIE RSPCIE

Default

0 0 0 0 0 0 0 0

Bit 7: Receive FCS Errored Packet Interrupt Enable (REPIE). This bit enables an interrupt if the REPL bit in

the

LI.RPPSRL

register is set.

0 = interrupt disabled

1 = interrupt enabled

Bit 6: Receive Aborted Packet Interrupt Enable (RAPIE). This bit enables an interrupt if the RAPL bit in the

LI.RPPSRL

register is set.

0 = interrupt disabled

1 = interrupt enabled

Bit 5: Receive Invalid Packet Detected Interrupt Enable (RIPDIE). This bit enables an interrupt if the RIPDL bit

in the

LI.RPPSRL

register is set.

0 = interrupt disabled

1 = interrupt enabled

Bit 4: Receive Small Packet Detected Interrupt Enable (RSPDIE). This bit enables an interrupt if the RSPDL

bit in the

LI.RPPSRL

register is set.

0 = interrupt disabled

1 = interrupt enabled

Bit 3: Receive Large Packet Detected Interrupt Enable (RLPDIE). This bit enables an interrupt if the RLPDL bit

in the

LI.RPPSRL

register is set.

0 = interrupt disabled

1 = interrupt enabled

Bit 2: Receive FCS Errored Packet Count Interrupt Enable (REPCIE). This bit enables an interrupt if the

REPCL bit in the

LI.RPPSRL

register is set. Must be set low when the packets do not have an FCS appended.

0 = interrupt disabled

1 = interrupt enabled

Bit 1: Receive Aborted Packet Count Interrupt Enable (RAPCIE). This bit enables an interrupt if the RAPCL bit

in the

LI.RPPSRL

register is set.

0 = interrupt disabled

1 = interrupt enabled

Bit 0: Receive Size Violation Packet Count Interrupt Enable (RSPCIE). This bit enables an interrupt if the

RSPCL bit in the

LI.RPPSRL

register is set.

0 = interrupt disabled

1 = interrupt enabled