Maxim Integrated DS33Z41 User Manual

Page 137

DS33Z41 Quad IMUX Ethernet Mapper

137 of 167

Register Name:

SU.TxBytesOkCtr

Register Description:

MAC Bytes Transmitted OK Counter

Register Address:

030Ch (indirect)

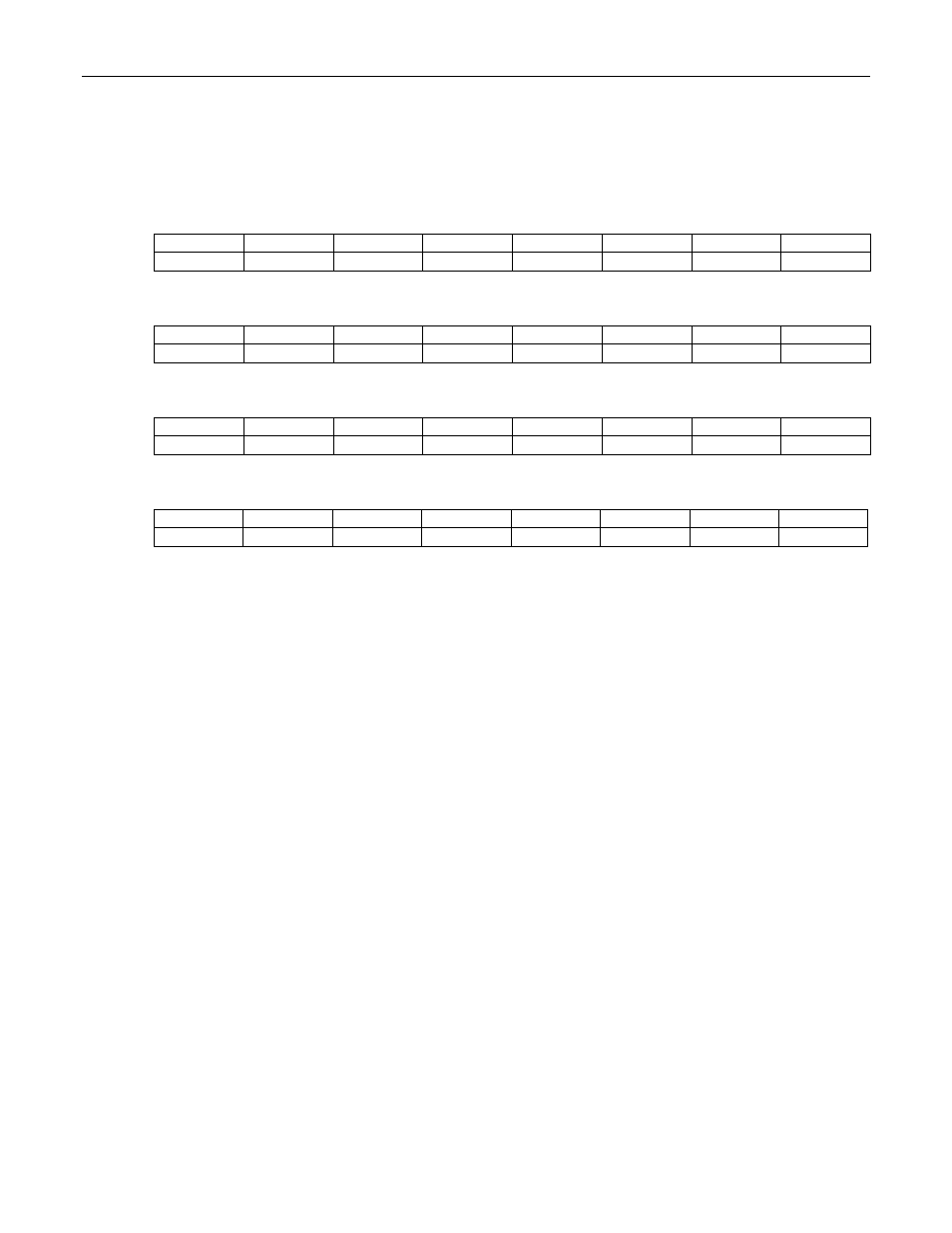

030Ch:

Bit

# 31 30 29 28 27 26 25 24

Name

TXBYTEOK31 TXBYTEOK30 TXBYTEOK29 TXBYTEOK28 TXBYTEOK27 TXBYTEOK26 TXBYTEOK25 TXBYTEOK24

Default

0 0 0 0 0 0 0 0

030Dh:

Bit

# 23 22 21 20 19 18 17 16

Name

TXBYTEOK23 TXBYTEOK22 TXBYTEOK21 TXBYTEOK20 TXBYTEOK19 TXBYTEOK18 TXBYTEOK17 TXBYTEOK16

Default

0 0 0 0 0 0 0 0

030Eh:

Bit

# 15 14 13 12 11 10 09 08

Name

TXBYTEOK15 TXBYTEOK14 TXBYTEOK13 TXBYTEOK12 TXBYTEOK11 TXBYTEOK10 TXBYTEOK9 TXBYTEOK8

Default

0 0 0 0 0 0 0 0

030Fh:

Bit

# 07 06 05 04 03 02 01 00

Name

TXBYTEOK7 TXBYTEOK6 TXBYTEOK5 TXBYTEOK4 TXBYTEOK3 TXBYTEOK2 TXBYTEOK1 TXBYTEOK0

Default

0 0 0 0 0 0 0 0

Bits 31 to 0: Bytes Transmitted OK Counter (TXBYTEOK31 to TXBYTEOK0). 32-bit value indicating the

number of bytes transmitted and determined to be valid. Each time a valid byte is transmitted, this counter is

incremented by 1. This counter resets only upon device reset, does not saturate, and rolls over to zero upon

reaching the maximum value. The user should ensure that the measurement period is less than the minimum

length of time required for the counter to increment 2^32-1 times at the maximum frame rate. The user should

store the value from the beginning of the measurement period for later calculations, and take into account the

possibility of a rollover occurring.