Drawing legend, Interrup t pin – Maxim Integrated DS33Z41 User Manual

Page 30

DS33Z41 Quad IMUX Ethernet Mapper

30 of 167

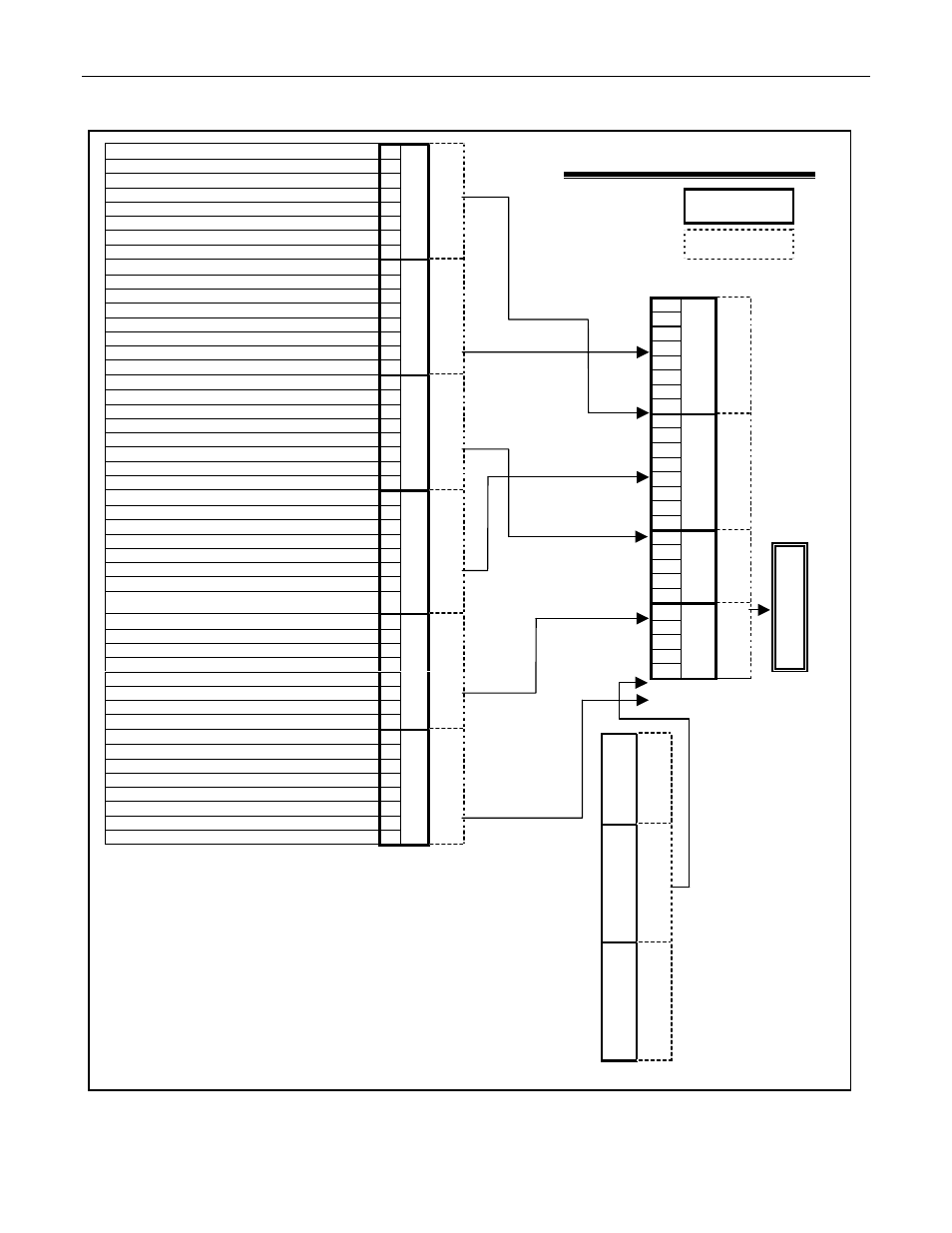

Figure 8-2. Device Interrupt Information Flow Diagram

Receive FCS Errored Packet

7

Receive Aborted Packet

6

Receive Invalid Packet Detected

5

Receive Small Packet Detected

4

Receive Large Packet Detected

3

Receive FCS Errored Packet Count

2

Receive Aborted Packet Count

1

Receive Size Violation Packet Count

0

LI.RPPSL

LI.RPPSRIE

7

6

5

4

3

2

1

Transmit Errored Packet Insertion Finished

0

LI.TPPSRL

LI.TPPSRIE

7

6

5

4

SAPI High is not equal to LI.TRX86SAPIH

3

SAPI Low is not equal to LI.TRX86SAPIL

2

Control is not equal to LI.TRX8C

1

Address is not equal to LI.TRX86A

0

LI.RX86S

LI.RX86LSIE

7

6

5

4

Transmit Queue FIFO Overflowed

3

Transmit Queue Overflow

2

Transmit Queue for Connection Exceeded Low Threshold

1

Transmit Queue for Connection Exceeded High

Threshold

0

LI.T

QCT

L

S

LI.T

QTIE

7

6

5

4

Receive Queue FIFO Overflowed

3

Receive Queue Overflow

2

Receive Queue for Connection Exceeded Low Threshold

1

Receive Queue for Connection Exceeded High Threshold

0

SU.Q

CRLS

SU.Q

RIE

7

6

5

4

Performance Monitor Update

3

Bit Error Detected

2

Bit Error Count

1

Out Of Synchronization

0

BSRL

BSRIE

Drawing Legend:

Interrupt Status

Registers

Register Name

Interrupt Enable

Registers

Register Name

Interrup

t Pin

7

6

5

4

3

2

1

0

GL.TRQ

IS

GL.TRQ

IE

7

6

5

4

3

2

1

0

GL.L

IS

GL.L

IE

...

3

2

1

0

GL.SIS

GL.SIE

...

3

2

1

0

GL.IBIS

GL.IBIE

GL.IMXS

LS

GL.IMXS

IE

GL.IMXDFDELS

GL.IMXDFE

IE

GL.IMX

OOF

L

S

GL.IMX

OOF

IE