Maxim Integrated DS33Z41 User Manual

Page 67

DS33Z41 Quad IMUX Ethernet Mapper

67 of 167

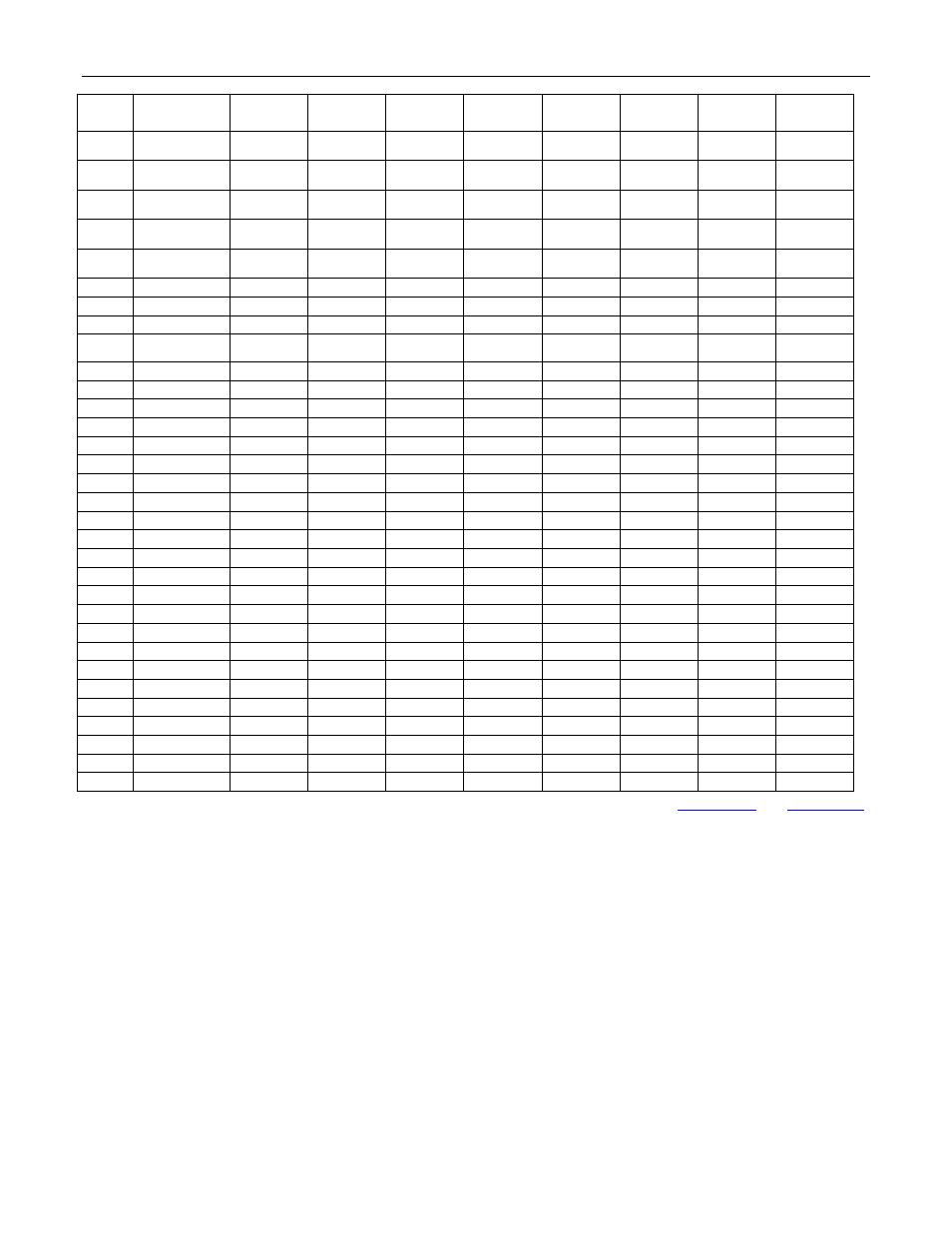

A

DDR

N

AME

B

IT

7

B

IT

6

B

IT

5

B

IT

4

B

IT

3

B

IT

2

B

IT

1

B

IT

0

110h

RESERVED –

initialize to FF

- - - - - - - -

111h

RESERVED –

initialize to FF

- - - - - - - -

112h

RESERVED –

initialize to FF

- - - - - - - -

113h

RESERVED –

initialize to FF

- - - - - - - -

200h

SU.RxFrmCtr

31:24

RXFRMC31 RXFRMC30 RXFRMC29 RXFRMC28 RXFRMC27 RXFRMC26 RXFRMC25 RXFRMC24

201h

23:16

RXFRMC23 RXFRMC22 RXFRMC21 RXFRMC20 RXFRMC19 RXFRMC18 RXFRMC17 RXFRMC16

202h

15:8

RXFRMC15 RXFRMC14 RXFRMC13 RXFRMC12 RXFRMC11 RXFRMC10 RXFRMC9 RXFRMC8

203h

7:0

RXFRMC7 RXFRMC6 RXFRMC5 RXFRMC4 RXFRMC3 RXFRMC2 RXFRMC1 RXFRMC0

204h

SU.RxFrmOKCtr

31:24

RXFRMOK31 RXFRMOK30 RXFRMOK29 RXFRMOK28 RXFRMOK27 RXFRMOK26 RXFRMOK25 RXFRMOK24

205h

23:16

RXFRMOK23 RXFRMOK22 RXFRMOK21 RXFRMOK20 RXFRMOK19 RXFRMOK18 RXFRMOK17 RXFRMOK16

206h

15:8

RXFRMOK15 RXFRMOK14 RXFRMOK13 RXFRMOK12 RXFRMOK11 RXFRMOK10 RXFRMOK9 RXFRMOK8

207h

7:0

RXFRMOK7 RXFRMOK6 RXFRMOK5 RXFRMOK4 RXFRMOK3 RXFRMOK2 RXFRMOK1 RXFRMOK0

300h

SU.TxFrmCtr

TXFRMC31 TXFRMC30 TXFRMC29 TXFRMC28 TXFRMC27 TXFRMC26 TXFRMC25 TXFRMC24

301h

23:16

TXFRMC23 TXFRMC22 TXFRMC21 TXFRMC20 TXFRMC19 TXFRMC18 TXFRMC17 TXFRMC16

302h

15:8

TXFRMC15 TXFRMC14 TXFRMC13 TXFRMC12 TXFRMC11 TXFRMC10 TXFRMC9 TXFRMC8

303h

7:0

TXFRMC7 TXFRMC6 TXFRMC5 TXFRMC4 TXFRMC3 TXFRMC2 TXFRMC1 TXFRMC0

308h

SU.TxBytesCtr

TXBYTEC31 TXBYTEC30 TXBYTEC29 TXBYTEC28 TXBYTEC27 TXBYTEC26 TXBYTEC25 TXBYTEC24

309h

23:16

TXBYTEC23 TXBYTEC22 TXBYTEC21 TXBYTEC20 TXBYTEC19 TXBYTEC18 TXBYTEC17 TXBYTEC16

30Ah

15:8

TXBYTEC15 TXBYTEC14 TXBYTEC13 TXBYTEC12 TXBYTEC11 TXBYTEC10 TXBYTEC9 TXBYTEC8

30Bh

7:0

TXBYTEC7 TXBYTEC6 TXBYTEC5 TXBYTEC4 TXBYTEC3 TXBYTEC2 TXBYTEC1 TXBYTEC0

30Ch

SU.TxBytesOkCtr TXBYTEOK31 TXBYTEOK30 TXBYTEOK29 TXBYTEOK28 TXBYTEOK27 TXBYTEOK26 TXBYTEOK25 TXBYTEOK24

30Dh

23:16

TXBYTEOK23 TXBYTEOK22 TXBYTEOK21 TXBYTEOK20 TXBYTEOK19 TXBYTEOK18 TXBYTEOK17 TXBYTEOK16

30Eh

15:8

TXBYTEOK15 TXBYTEOK14 TXBYTEOK13 TXBYTEOK12 TXBYTEOK11 TXBYTEOK10 TXBYTEOK9 TXBYTEOK8

30Fh

7:0

TXBYTEOK7 TXBYTEOK6 TXBYTEOK5 TXBYTEOK4 TXBYTEOK3 TXBYTEOK2 TXBYTEOK1 TXBYTEOK0

334h

SU.TxFrmUndr

TXFRMU31 TXFRMU30 TXFRMU29 TXFRMU28 TXFRMU27 TXFRMU26 TXFRMU25 TXFRMU24

335h

23:16

TXFRMU23 TXFRMU22 TXFRMU21 TXFRMU20 TXFRMU19 TXFRMU18 TXFRMU17 TXFRMU16

336h

15:8

TXFRMU15 TXFRMU14 TXFRMU13 TXFRMU12 TXFRMU11 TXFRMU10 TXFRMU9 TXFRMU8

337h

7:0

TXFRMU7 TXFRMU6 TXFRMU5

TXFRMU4 TXFRMU3 TXFRMU2 TXFRMU1 TXFRMU0

338h

SU.TxBdFrmCtr

TXFRMBD31 TXFRMBD30 TXFRMBD29 TXFRMBD28 TXFRMBD27 TXFRMBD26 TXFRMBD25 TXFRMBD24

339h

23:16

TXFRMBD23 TXFRMBD22 TXFRMBD21 TXFRMBD20 TXFRMBD19 TXFRMBD18 TXFRMBD17 TXFRMBD16

33Ah

15:8

TXFRMBD15 TXFRMBD14 TXFRMBD13 TXFRMBD12 TXFRMBD11 TXFRMBD10 TXFRMBD9 TXFRMBD8

33Bh

7:0

TXFRMBD7 TXFRMBD6 TXFRMBD5 TXFRMBD4 TXFRMBD3 TXFRMBD2 TXFRMBD1 TXFRMBD0

Note that the addresses in the table above are the indirect addresses that must be provided to the

SU.MACAWH

and

SU.MACAWL

.

All unused and reserved locations must be initialized to zero for proper operation unless specifically noted otherwise.