Maxim Integrated DS33Z41 User Manual

Page 87

DS33Z41 Quad IMUX Ethernet Mapper

87 of 167

Register Name:

RBECB0R

Register Description:

Receive Bit Error Count Byte 0 Register

Register Address:

94h

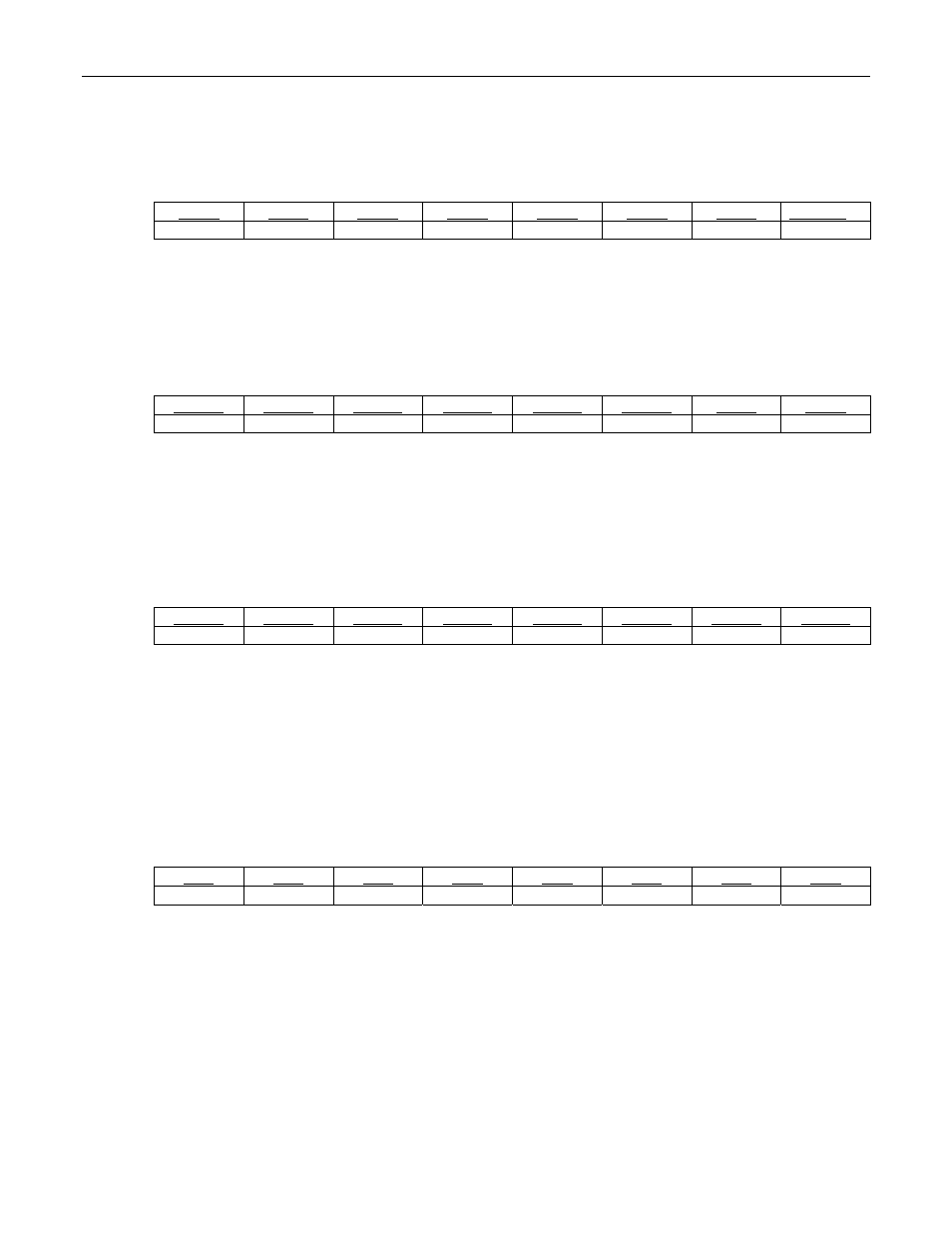

Bit

# 7 6 5 4 3 2 1 0

Name BEC7 BEC6 BEC5 BEC4 BEC3 BEC2 BEC1

BEC0

Default

0 0 0 0 0 0 0 0

Bits 7 to 0: Bit Error Count (BEC7 to BEC0). Lower eight bits of 24 bits. Register description below.

Register Name:

RBECB1R

Register Description:

Receive Bit Error Count Byte 1 Register

Register Address:

95h

Bit

# 7 6 5 4 3 2 1 0

Name BEC15 BEC14 BEC13 BEC12 BEC11 BEC10 BEC9 BEC8

Default

0 0 0 0 0 0 0 0

Bits 7 to 0: Bit Error Count (BEC15 to BEC8). Eight bits of a 24 bit value. Register description below.

Register Name:

RBECR2

Register Description:

Receive Bit Error Count Byte 2 Register

Register Address:

96h

Bit

# 7 6 5 4 3 2 1 0

Name BEC23 BEC22 BEC21 BEC20 BEC19 BEC18 BEC17 BEC16

Default

0 0 0 0 0 0 0 0

Bits 7 to 0: Bit Error Count (BEC23 to BEC16). Upper 8-bits of the register.

Bit Error Count (BEC23 to BEC0). These 24 bits indicate the number of bit errors detected in the incoming data

stream. This count stops incrementing when it reaches a count of FF FFFFh. The associated bit error counter will

not incremented when an OOS condition exists.

Register Name:

RBCB0

Register Description:

Receive Bit Count Byte 0 Register

Register Address:

98h

Bit

# 7 6 5 4 3 2 1 0

Name BC7 BC6 BC5 BC4 BC3 BC2 BC1 BC0

Default

0 0 0 0 0 0 0 0

Bits 7 to 0: Bit Count (BC7 to BC0). Eight bits of a 32-bit value. Register description below.