Figure 8-3. imux interface to t1/e1 transceivers, Sequence 01, Sequence 02 – Maxim Integrated DS33Z41 User Manual

Page 32

DS33Z41 Quad IMUX Ethernet Mapper

32 of 167

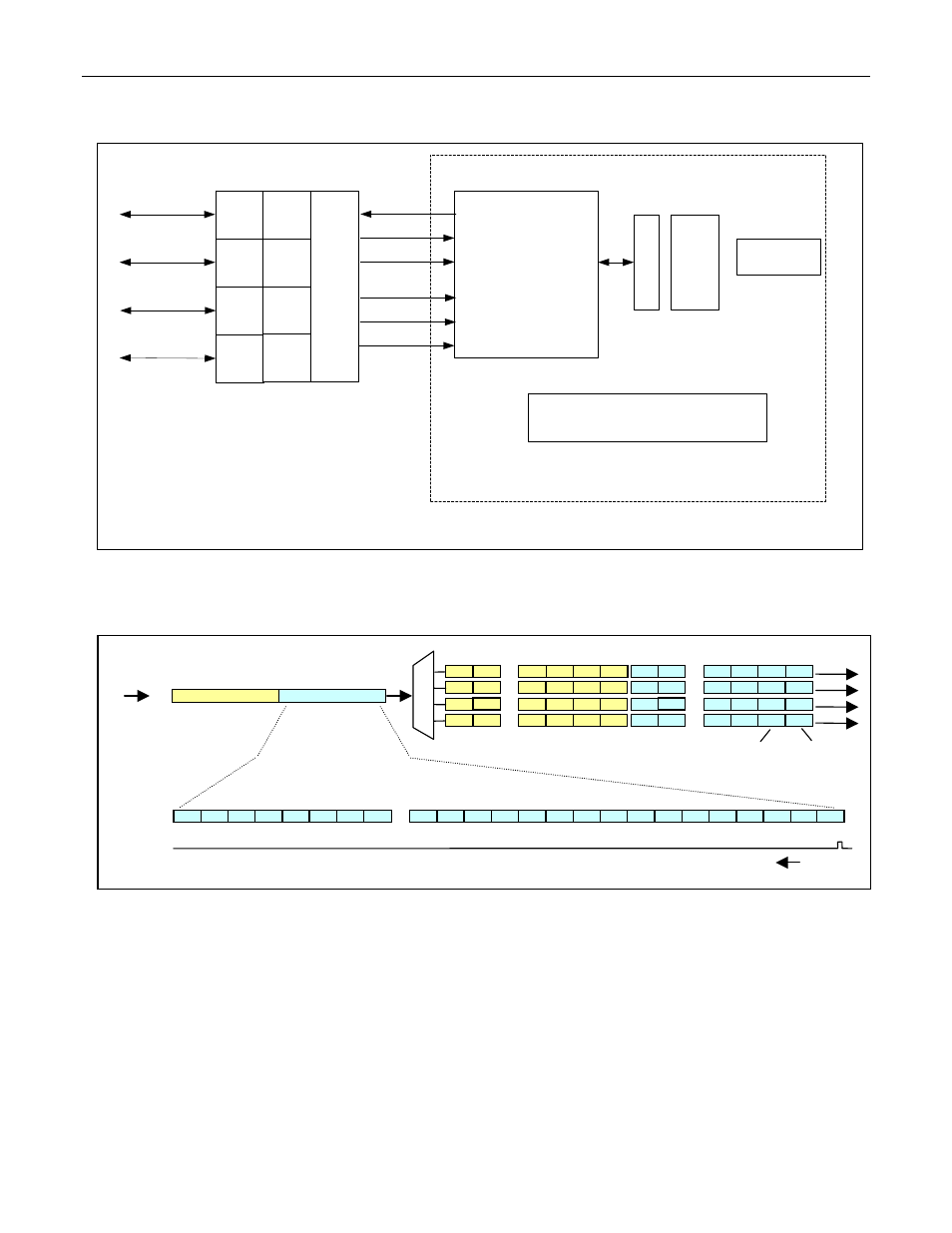

Figure 8-3. IMUX Interface to T1/E1 Transceivers

T1E1

T1E1

T1E1

T1E1

LIU

LIU

LIU

LIU

Framer

Framer

Framer

Framer

I

B

O

TSER

RSER

TSYNC

RSYNC

Line 1

IMUX

Ethernet Port

Arbiter

SDRAM

Interface

H

D

L

C

T1E1

T1E1

TCLKI

RCLKI

Figure 8-4. Diagram of Data Transmission with IMUX Operation

. . .

. . .

. . .

. . .

Sequence 01

L1 03

L2 03

L3 03

L4 03

L1 04

L2 04

L3 04

L4 04

L1 31

L2 31

L3 31

L4 31

L1 32

L2 32

L3 32

L4 32

s01

s01

s01

s01

xxxx

xxxx

xxxx

xxxx

. . .

. . .

. . .

. . .

Sequence 02

L1 03

L2 03

L3 03

L4 03

L1 04

L2 04

L3 04

L4 04

L1 31

L2 31

L3 31

L4 31

L1 32

L2 32

L3 32

L4 32

s02

s02

s02

s02

xxxx

xxxx

xxxx

xxxx

LINK 1

LINK 2

LINK 3

LINK 4

FRAM

ER IBO

128 Byte Sequence 01

128 Byte Sequence 02

. . .

. . .

L1 03

L2 03

L3 03

L4 03

L1 04

L2 04

L3 04

L4 04

L1 31

L2 31

L3 31

L4 31

L1 32

L2 32

L3 32

L4 32

s01

s01

s01

s01

xxxx

xxxx

xxxx

xxxx

Byte Sequence Detail

. . .

N

N+1

N+2

N+3

N+4

N+5

N+6

N+7

N+119

N+120

. . .

From TSER

Encapsulated

Packet Byte:

Data on IBO Bus

TSYNC:

Time

Sequence

Numbers

Signaling

Channel

- DS80C390 (58 pages)

- DS5001FP (26 pages)

- MAX1416 (14 pages)

- MAX5865 (18 pages)

- MAX1202 (7 pages)

- USBTO232 (31 pages)

- HFAN-09.5.0: Pattern Creator/Converter Software (8 pages)

- MAX-IDE MAXQ Microcontrollers (11 pages)

- MAX6876 Power-Supply Tracker/Sequencer (6 pages)

- MAX6877 Power-Supply Tracker/Sequencer (3 pages)

- 78Q8430 ARM9(920T) Linux Driver Diagnostic Guide (19 pages)

- 78Q8430 Software Driver (54 pages)

- 78Q8430 ST 5100/OS-20 with NexGen TCP/IP Stack (28 pages)

- 6612_OMU_S2_URT_V1_13 (56 pages)

- 6612_OMU_S2+2_URT_V1_14 (58 pages)

- 71M6511 Power Meter IC Family Software (137 pages)

- 71M65xx ADM51 ICE Safety Notice (2 pages)

- 71M6511 2-Layer Demo Board (2 pages)

- 71M6511 4-Layer Demo Board (2 pages)

- 78Q8430 Linux Driver ARM Platform (22 pages)

- 71M6513 Demo Board (2 pages)

- 71M6521DE Energy Meter IC Family Software (138 pages)

- 71M6521 Demo Board (2 pages)

- 71M6531 Demo Board (2 pages)

- 71M6531 Energy Meter IC Family Software (116 pages)

- 71M6533 Demo Board (2 pages)

- 71M6534H Demo Board (2 pages)

- 71M6515H Demo Board (2 pages)

- 73S1209F Evaluation Board (2 pages)

- 73S12xxF (38 pages)

- 73S12xxF Software (93 pages)

- 73S1210F Evaluation Board Lite (2 pages)

- 73S1210F Evaluation Board (2 pages)

- 73S1210F Multi-SAM Evaluation Board Lite (2 pages)

- 73S12xxF USB-CCID Linux DFU Host Application (8 pages)

- 73S1215F Device Firmware Upgrade Host Driver/Application (10 pages)

- 73S12xxF USB-CCID Host GUI (22 pages)

- 73S1215F Windows XP 32 USB CCID and DFU Drivers (15 pages)

- 73S1215F CCID USB Linux Driver (16 pages)

- 73S1215F Evaluation Board (2 pages)

- 73S1215F Evaluation Board Lite (2 pages)

- 73S1217F Evaluation Board (2 pages)

- 73S1217F Evaluation Board Lite (2 pages)

- MAXQ Family (216 pages)