Maxim Integrated DS33Z41 User Manual

Page 78

DS33Z41 Quad IMUX Ethernet Mapper

78 of 167

Register Name:

GL.IMXOOFLS

Register Description:

Inverse MUX Out Of Frame Latched Status

Register Address:

1Fh

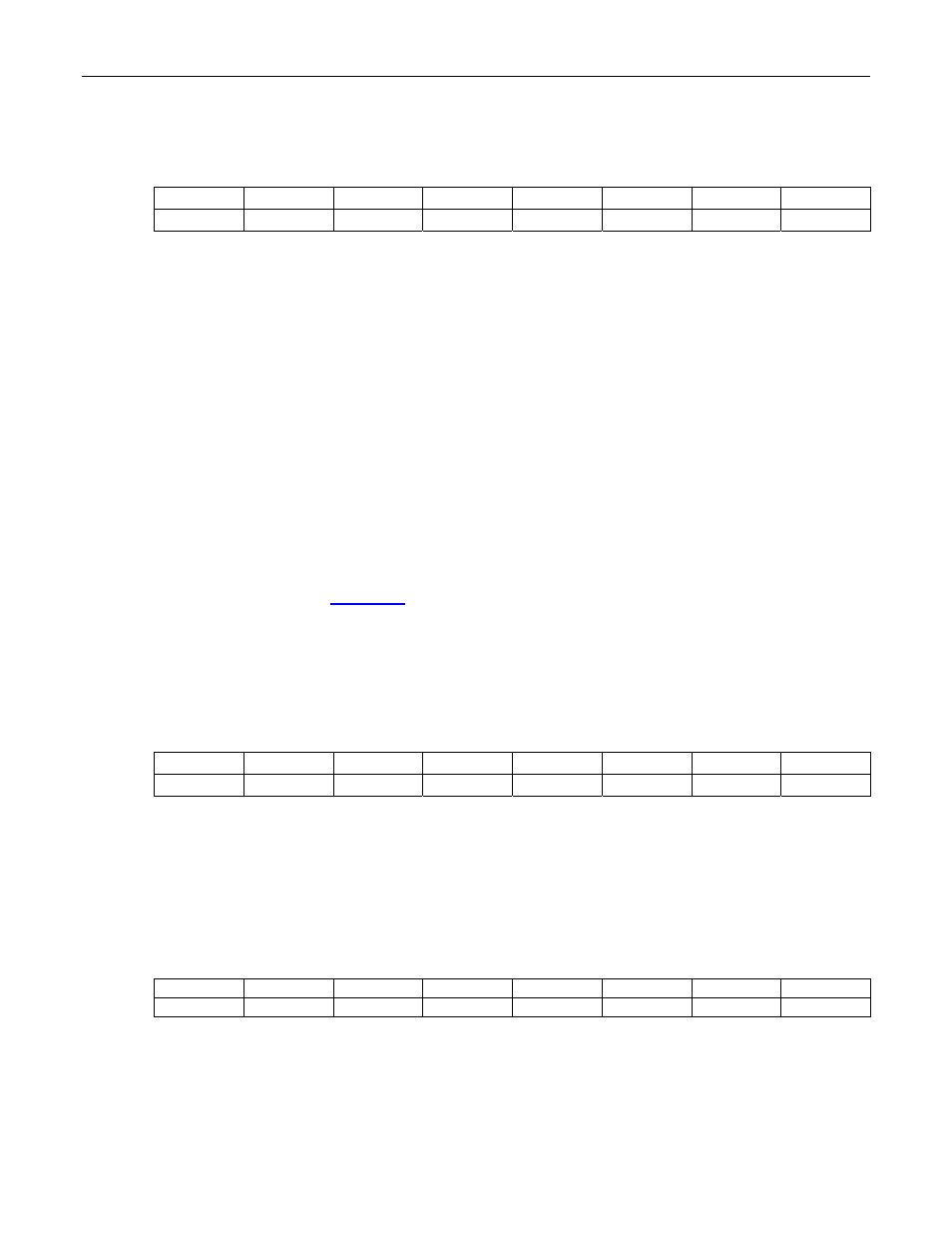

Bit #

7 6 5 4 3 2 1 0

Name

TOOFLS4 OOFLS3 TOOFLS2 TOOFLS1 ROOFL4 ROOFL3 ROOFLS2 ROOFLS1

Default

0 0 0 0 0 0 0 0

Bit 7: IMUX Transmit OOF Latched Status 4 (TOOFLS4). This is a latched bit for Transmit OOF, this bit is set if

the distant end is out of frame.

Bit 6: IMUX Transmit OOF Latched Status 3 (TOOFLS3). This is a latched bit for Transmit OOF, this bit is set if

the distant end is out of frame.

Bit 5: IMUX Transmit Sync Latched Status 2 (TOOFLS2). This is a latched bit for Transmit OOF, this bit is set if

the distant end is out of frame.

Bit 4: IMUX Transmit Sync Latched Status 1 (TOOFLS1). This is a latched bit for Transmit OOF , this bit is set

if the distant end is out of frame.

Bit 3: IMUX Receive Sync Latched Status 4 (ROOFLS4). This is a latched bit for Receiver OOF, this bit is set if

the receiver end is out of frame.

Bit 2: IMUX Receive Sync Latched Status 3 (ROOFLS3). This is a latched bit for Receiver OOF, this bit is set if

the receiver end is out of frame.

Bit 1: IMUX Receive Sync Latched Status 2 (ROOFLS2). This is a latched bit for Receiver OOF, this bit is set if

the receiver end is out of frame.

Bit 0: IMUX Receive Sync Latched Status 1 (ROOFLS1). This is a latched bit for Receiver OOF, this bit is set if

the receiver end is out of frame.

Note that the user must clear the

GL.IMXCN

.SENDE bit to stop data transmission when an OOF condition is

detected. The user must re-initiate the handshaking procedure for re-establishment of communication.

Register Name:

GL.BISTEN

Register Description:

BIST Enable

Register Address:

20h

Bit #

7 6 5 4 3 2 1 0

Name

— — — — — — —

BISTE

Default

0 0 0 0 0 0 0 0

Bit 0: BIST Enable (BISTE). If this bit is set the DS33Z41 performs BIST test on the SDRAM. Normal data

communication is halted while BIST enable is high. The user must reset the DS33Z41 after completion of BIST

test before normal dataflow can begin.

Register Name:

GL.BISTPF

Register Description:

BIST PassFail

Register Address:

21h

Bit

# 7 6 5 4 3 2 1 0

Name — — — — — —

BISTDN

BISTPF

Default

0 0 0 0 0 0 0 0

Bit 1: BIST DONE (BISTDN). If this bit is set to 1, the DS33Z41 has completed the BIST Test initiated by BISTE.

The pass fail result is available in BISTPF.