Ethernet mac, Thernet – Maxim Integrated DS33Z41 User Manual

Page 46

DS33Z41 Quad IMUX Ethernet Mapper

46 of 167

8.14 Ethernet MAC

Indirect addressing is required to access the MAC register settings. Writing to the MAC registers requires the

SU.MACWD0

-3 registers to be written with 4 bytes of data. The address must be written to

SU.MACAWL

and

SU.MACAWH

. A write command is issued by writing a zero to

SU.MACRWC

.MCRW and a one to

SU.MACRWC

.MCS (MAC command status). MCS is cleared by the DS33Z41 when the operation is complete.

Reading from the MAC registers requires the

SU.MACRADH

and

SU.MACRADL

registers to be written with the

address for the read operation. A read command is issued by writing a one to

SU.MACRWC

.MCRW and a zero to

SU.MACRWC

.MCS.

SU.MACRWC

.MCS is cleared by the DS33Z41 when the operation is complete. After MCS

is clear, valid data is available in

SU.MACRD0

-

SU.MACRD3

. Note that only one operation can be initiated (read

or write) at one time. Data cannot be written or read from the MAC registers until the MCS bit has been cleared by

the device. The MAC Registers are detailed in the following table.

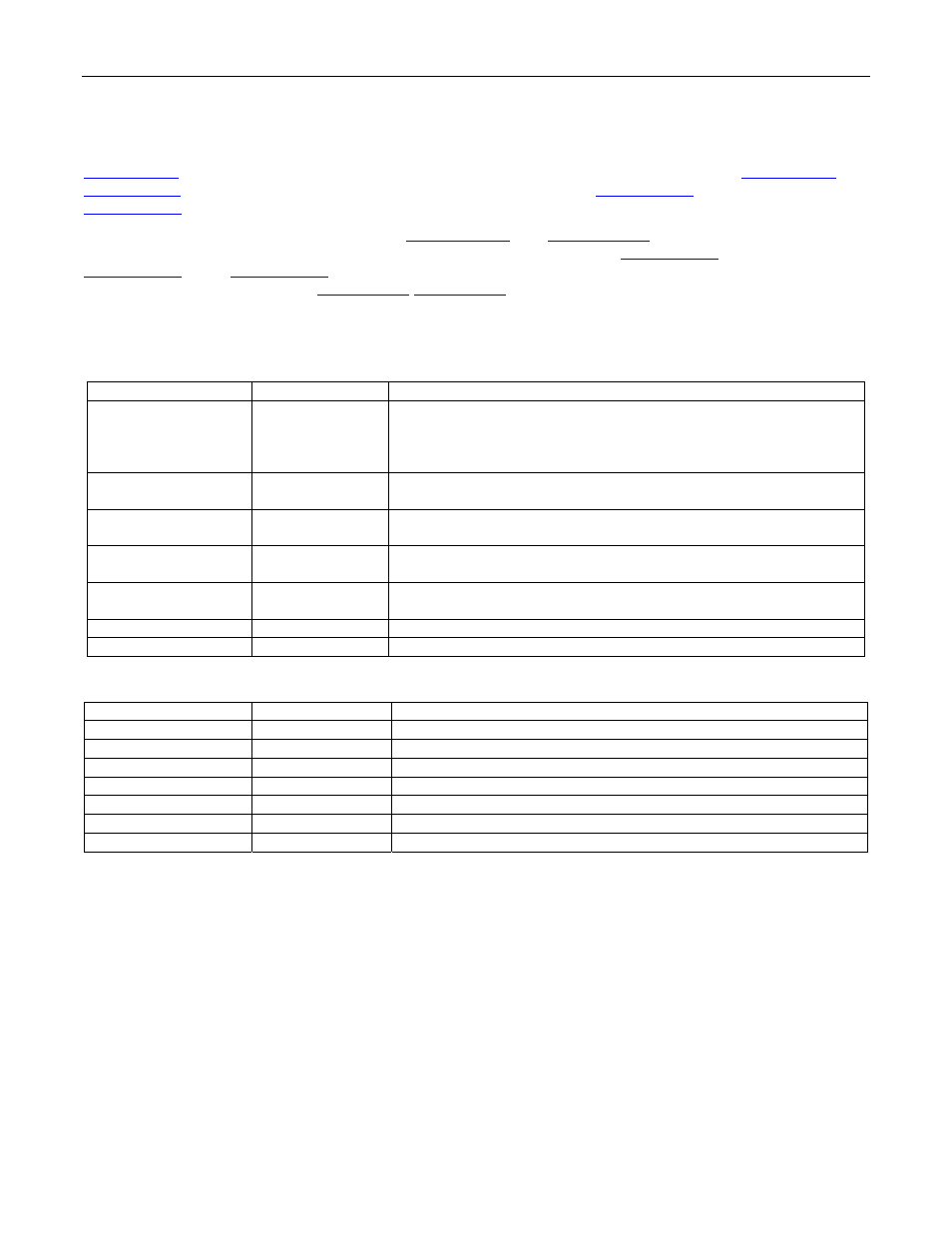

Table 8-8. MAC Control Registers

ADDRESS REGISTER

DESCRIPTION

0000h-0003h SU.MACCR

MAC Control Register. This register is used for programming full

duplex, half duplex, promiscuous mode, and back-off limit for half

duplex. The transmit and receive enable bits must be set for the

MAC to operate.

0004h-0007h SU.MACAH

MAC Address High Register. This provides the physical address for

this MAC.

0008h-000Bh SU.MACAL

MAC Address Low Register. This provides the physical address for

this MAC.

0014h-0017h SU.MACMIIA

MII Address Register. The address for PHY access through the

MDIO interface.

0018h-001Bh SU.MACMIID

MII Data Register. Data to be written to (or read from) the PHY

through MDIO interface.

001Ch-001Fh

SU.MACFCR

Flow Control Register

0100h-0103h

SU.MMCCTRL MMC Control Register bit 0 for resetting the status counters

Table 8-9. MAC Status Registers

ADDRESS REGISTER

DESCRIPTION

0200h-0203h

SU.RxFrmCntr

All Frames Received counter

0204h-0207h

SU.RxFrmOKCtr Number of Received Frames that are Good

0300h-0303h

SU.TxFrmCtr

Number of Frames Transmitted

0308h-030Bh

SU.TxBytesCtr Number of Bytes Transmitted

030Ch-030Fh

SU.TxBytesOkCtr Number of Bytes Transmitted with good frames

0334h-0337h

SU.TxFrmUndr Transmit FIFO underflow counter

0338h-033Bh

SU.TxBdFrmsCtr Transmit Number of Frames Aborted