Functional timing, Mii and rmii interfaces, Rmii i – Maxim Integrated DS33Z41 User Manual

Page 140: Nterfaces, 10 functional timing, 1 mii and rmii interfaces, Figure 10-1. mii transmit functional timing

DS33Z41 Quad IMUX Ethernet Mapper

140 of 167

10 FUNCTIONAL TIMING

10.1 MII and RMII Interfaces

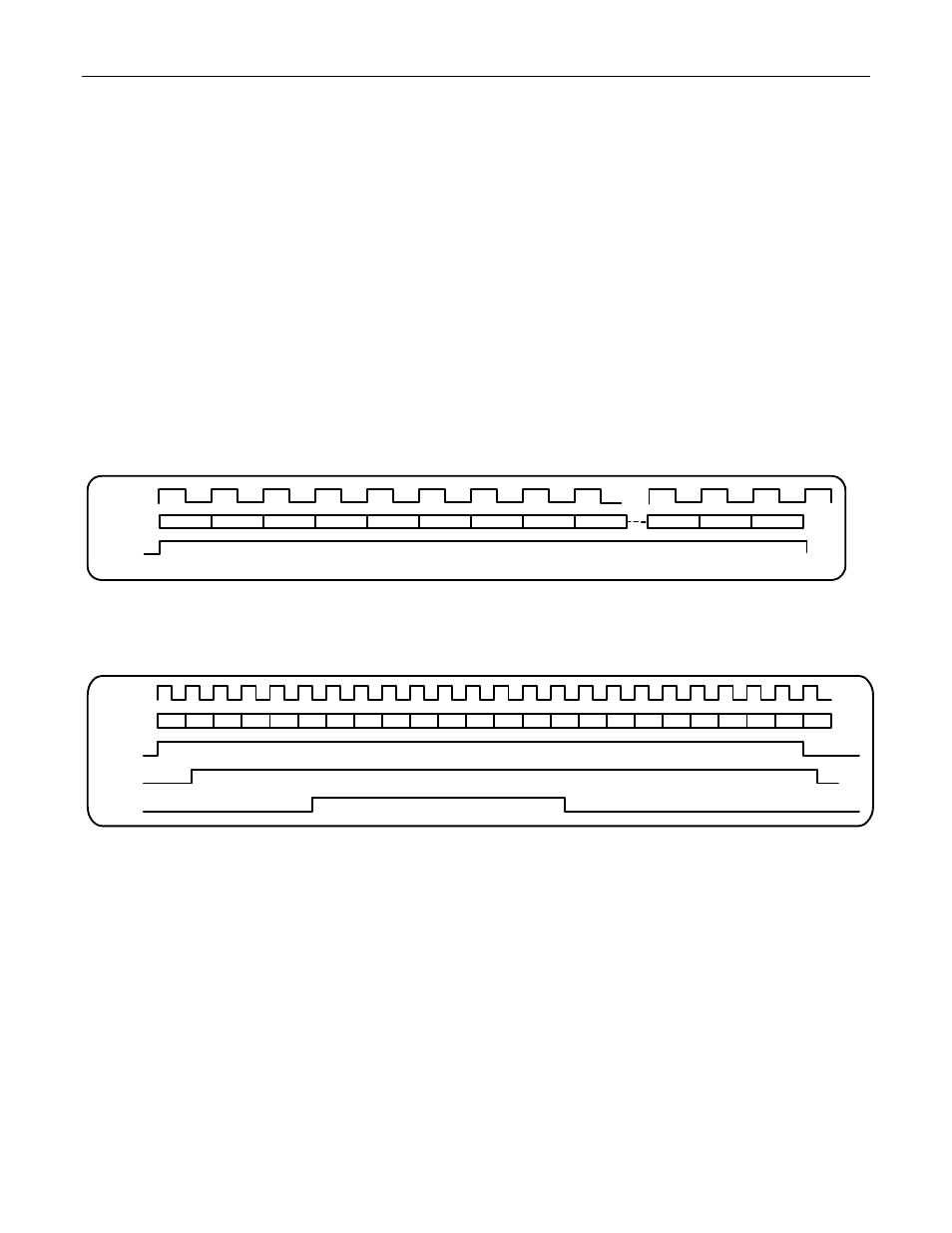

Each MII Interface Transmit Port has its own TX_CLK and data interface. The data TXD [3:0] operates

synchronously with TX_CLK. The LSB is presented first. TX_CLK should be 2.5MHz for 10Mbps operation and

25MHz for 100Mbps operation. TX_EN is valid at the same time as the first byte of the preamble. In DTE Mode

TX_CLK is input from the external PHY. In DCE Mode, the DS33Z41 provides TX_CLK, derived from an external

reference (SYSCLKI).

In Half-Duplex (DTE) Mode, the DS33Z41 supports CRS and COL signals. CRS is active when the PHY detects

transmit or receive activity. If there is a collision as indicated by the COL input, the DS33Z41 will replace the data

nibbles with jam nibbles. After a “random“ time interval, the packet is retransmitted. The MAC will try to send the

packet a maximum of 16 times. The jam sequence consists of 55555555h. Note that the COL signal and CRS can

be asynchronous to the TX_CLK and are only valid in half duplex mode.

Figure 10-1. MII Transmit Functional Timing

TXD[3:0]

TX_EN

TX_CLK

P

R

E

A

E

M

B

L

E

F

C

S

Figure 10-2. MII Transmit Half Duplex with a Collision Functional Timing

TXD[3:0]

TX_EN

TX_CLK

P

R

E

A

M

B

L

E

J

J

J

J

J

J

J

J

CRS

COL