NEC PD75402A User Manual

Page 98

87

CHAPTER 5. PERIPHERAL HARDWARE FUNCTIONS

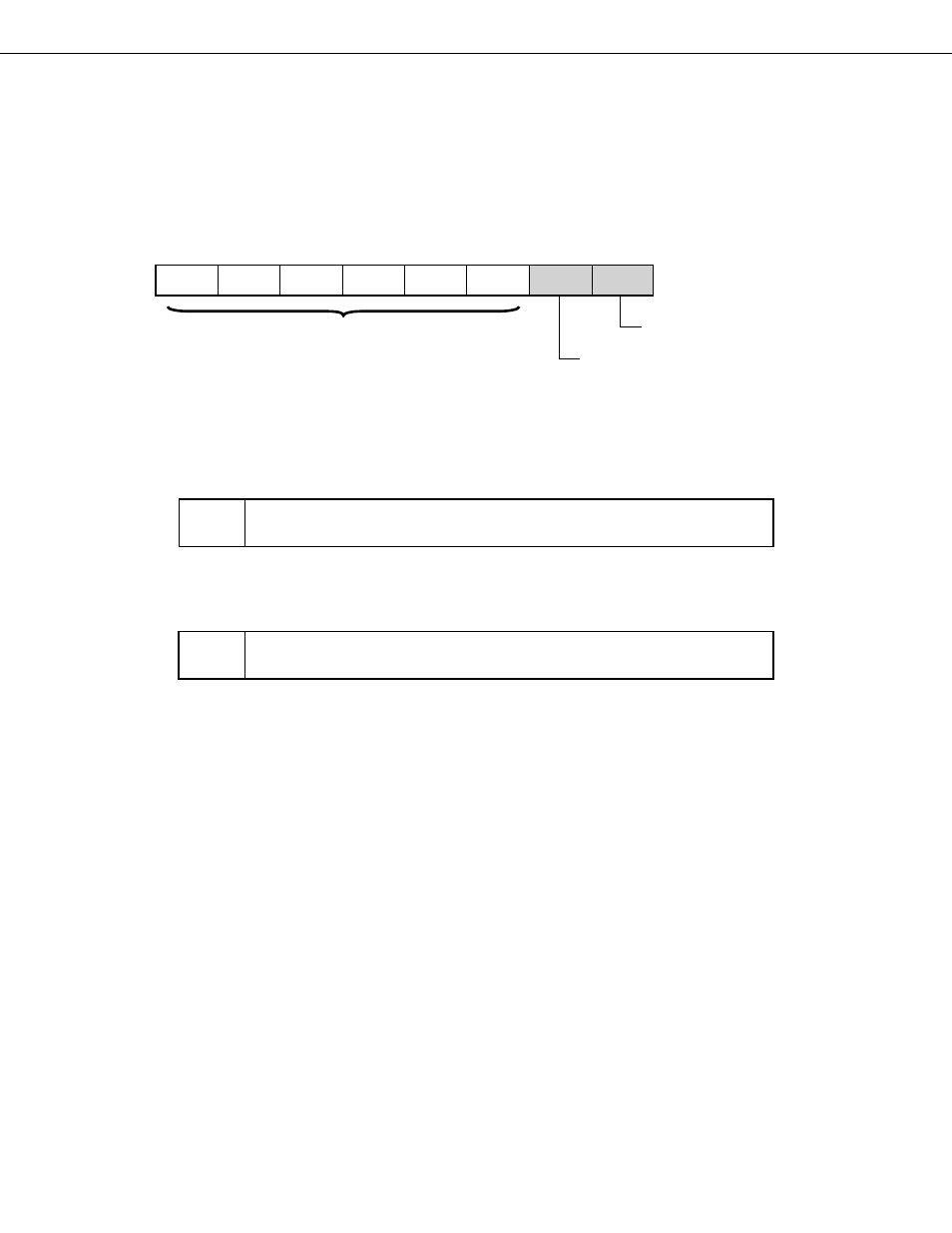

(b) Serial bus interface control register (SBIC)

When the 3-wire serial I/O mode is used, SBIC is set as shown below (see 5.5.3 (2) “Serial bus interface

control register” for full details of SBIC).

SBIC is manipulated by bit manipulation instructions.

Reset input clears the SBIC register to 00H.

The shaded area indicates bits used in the 3-wire serial I/O mode.

Address

7

6

5

4

3

2

1

0

Symbol

FE2H

BSYE

ACKD

ACKE

ACKT

CMDD

RELD

CMDT

RELT

SBIC

Bus Release Trigger Bit (W)

Command Trigger Bit (w)

Should not used in 3-wire serial I/O mode

Command trigger bit

CMDT

The command signal (CMD) Trigger output control bit. The SO latch is cleared (0) by setting

this bit (CMDT = 1), after which the CMDT bit is automatically cleared (0).

Remarks

(W)

Write only

Bus release trigger bit (W)

RELT

The command signal (REL) trigger output control bit. The SO latch is cleared (0) by setting

this bit (RELT = 1), after which the RELT bit is automatically cleared (0).

Note

Bits other than RELT and CMDT should not be used in the 3-wire serial I/O mode.