NEC PD75402A User Manual

Page 121

110

CHAPTER 5. PERIPHERAL HARDWARE FUNCTIONS

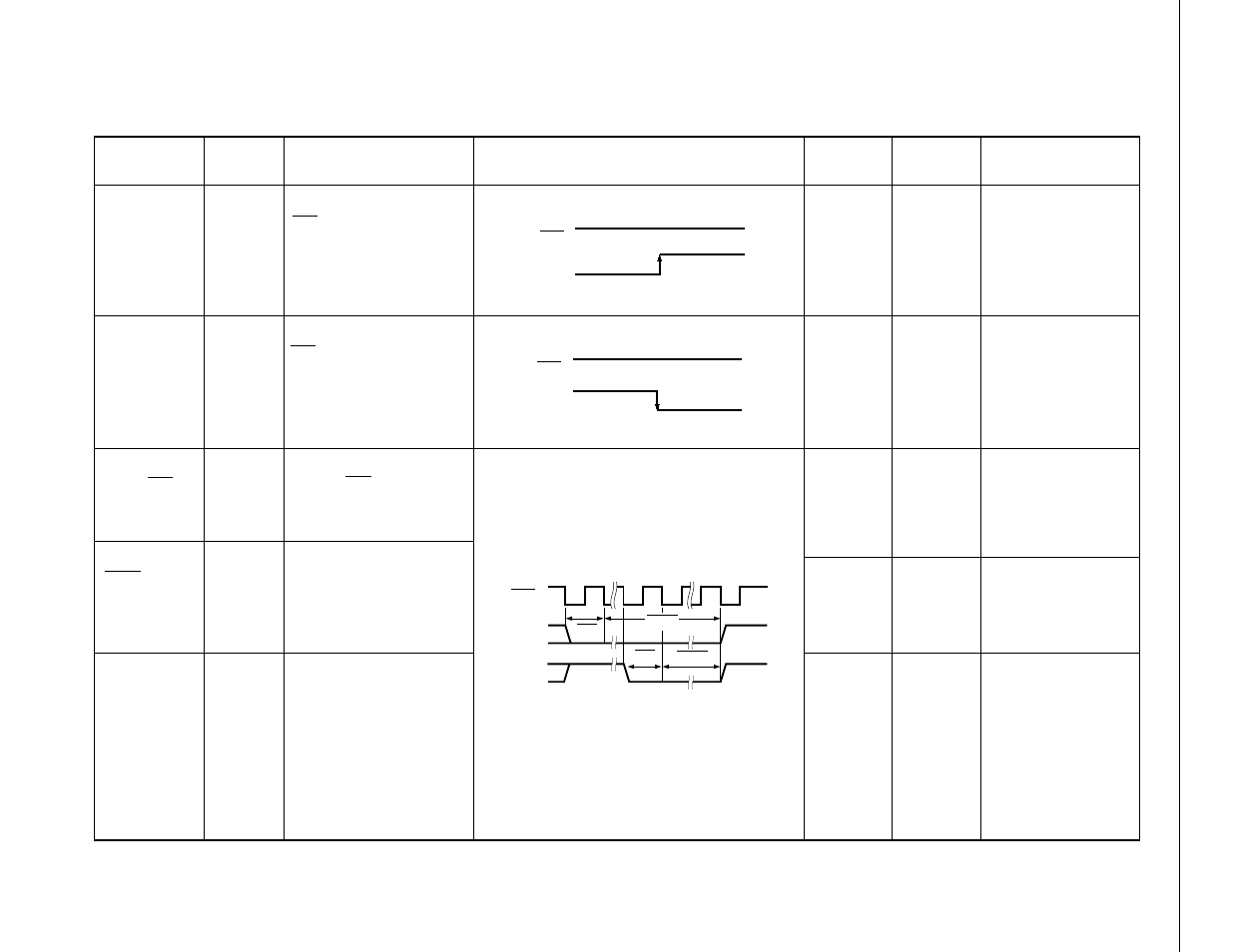

Table 5-8 Signals in SBI Mode (1/2)

Signal Name

Output

Device

Timing Chart

Definition

Output

Condition

Effect on

Flag

Meaning of

Signal

—

Outputs next CMD

signal and indicates

send data is address.

i)

After REL signal

output send data is

address.

ii) send data with no

REL signal output is

command.

Receive completion

Serial transmission/

reception disabled

because processing is in

progress.

Serial transmission/

reception enabled

SB0 rising edge when

SCK = 1

SB0 falling edge when

SCK = 1

Low-level signal output to

SB0 in 1 SCK clock intercal

after serial receive comple-

tion.

Low-level signal output to

SB0 after Acknowledge

signal.

High-level signal output to

SBO before start or after

completion of serial transfer.

Master

Master

Master/

slave

Slave

Slave

• RELD set

• CMDD

Cleared

• CMDD set

• ACKD set

• RELT set

• CMDT set

➀

ACKE = 1

➁

ACKE set

• BSYE = 1

➀

BSYE = 0

➁

Execution

of instruc-

tion to

write data

to SIO

(transfer

start

directive)

—

Bus release

signal (REL)

Command

signal (CMD)

Acknowledge

singnl (ACK)

Busy signal

(BUSY)

Ready signal

(READY)

“H”

SCK

SB0

“H”

SCK

SB0

9

ACK

D0

D0

SB0

SB0

SCK

ACK

BUSY

READY

READY

BUSY