NEC PD75402A User Manual

Page 91

80

CHAPTER 5. PERIPHERAL HARDWARE FUNCTIONS

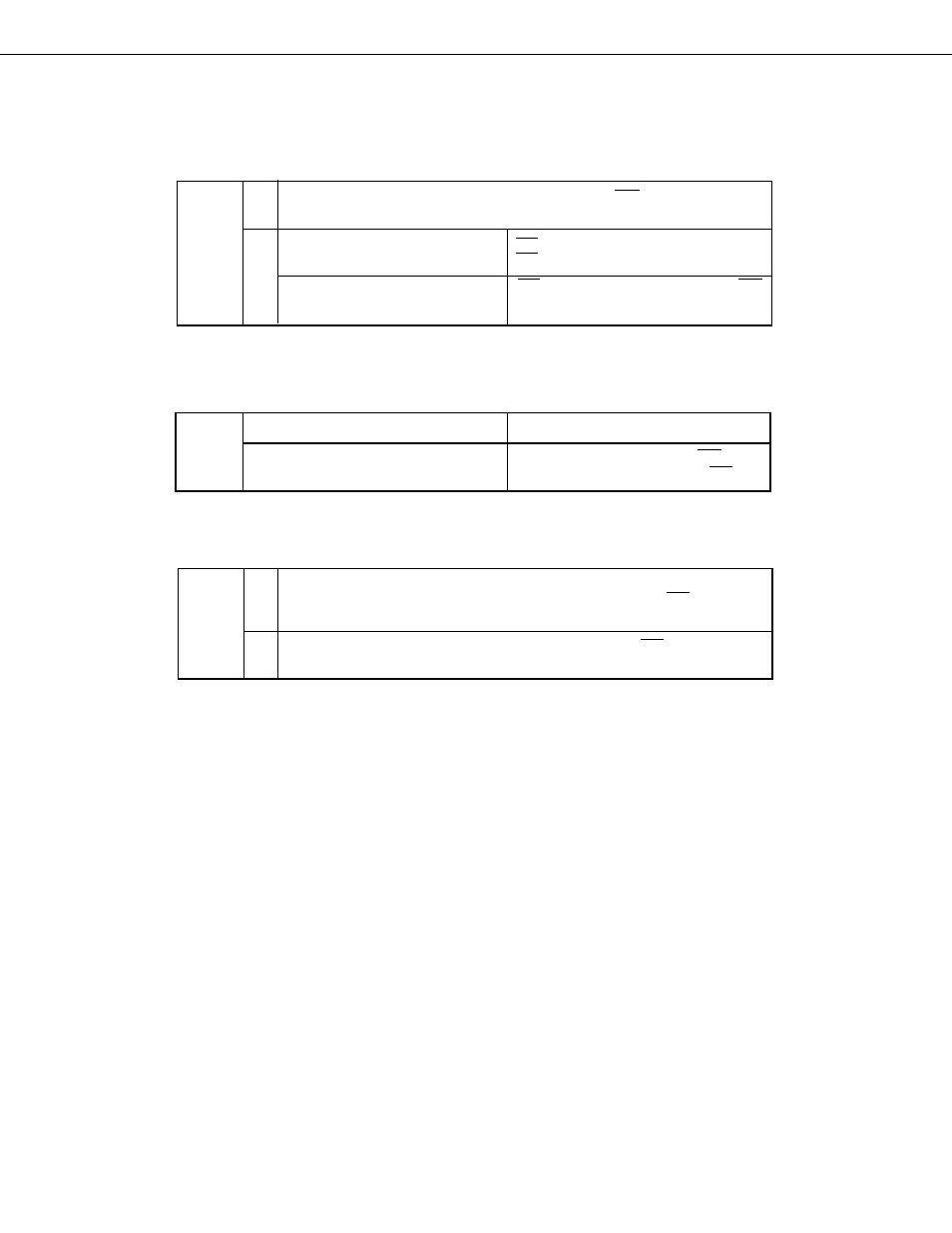

Fig. 5-26 Serial Bus Interface Control Register (SBIC) Format (3/3)

Acknowledge enable bit (R/W)

ACKE

When set before end of transfer

ACK is output is synchronization with the 9th

SCK clock cycle.

When set after end of transfer

ACK is output in synchronization with SCK

immediately after execution of the setting

instruction.

Disables automatic output of the acknowledge signal (ACK) (outpt by ACKT is

possibel).

0

1

Acknowledge detection flag (R)

Clearing Conditions (ACKD = 0)

Setting Condition (ACKD = 1)

➀

When a transfer is started

➁

When RESET is input

ACKD

When the acknowledge signal (ACK) is de-

tected (Synchronized with rise of SCK)

Busy enable bit (R/W)

Example

1.

To output the command signal.

SET1

CMDT

2.

To test RELD and CMDD, and perform different processing according to the type of receive data.

This interrupt routine is only performed when WUP = 1 and there is an address match.

SKF

RELD

;

Test RELD

BR

!ADRS

SKT

CMDD

;

Test CMDD

BR

!DATA

CMD

:

...............

;

Command interpretation

DATA :

...............

;

Data processing

ADRS :

...............

;

Address decoding

0

➀

Disablin of automatic busy signal output

➁

Busy signal output is stopped in synchronization with the fall of SCK immediately

after execution ofthe clearing instruction.

The busy signal is output in synchronization with the fall or SCK following the

acknowledge signal.

1

BSYE