NEC PD75402A User Manual

Page 37

CHAPTER 3. FEATURES OF ARCHITECTURE AND MEMORY MAP

26

P30

P61

P53

(i) SET1

CY

; CY

←

1

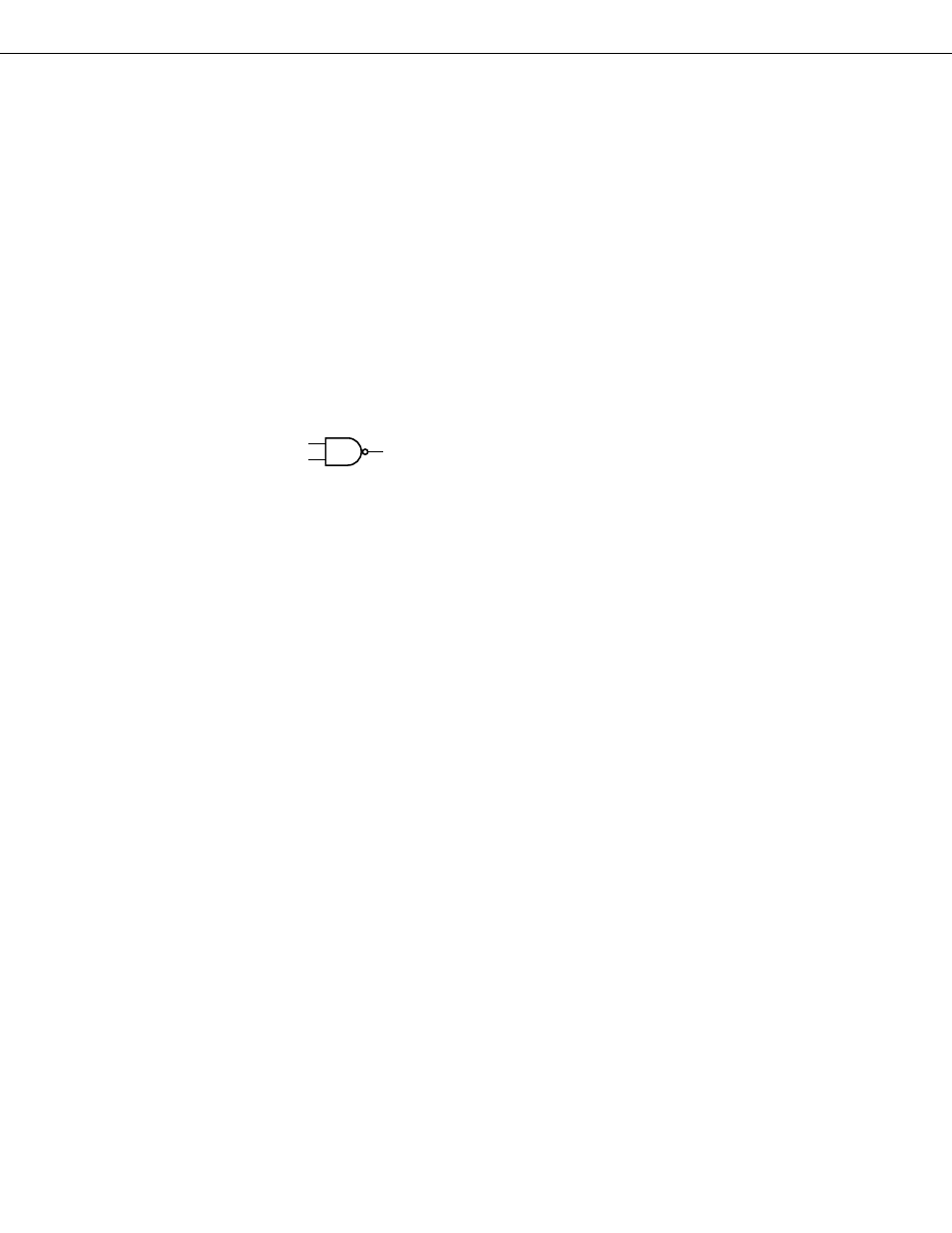

AND1

CY, PORT3. 0 ; CY

∧

P30

AND1

CY, PORT6. 1 ; CY

∧

P61

SKT

CY

; CY = 1?

BR

SETP

CLR1

PORT5. 3

;P53

←

0

.

.

SETP: SET1 PORT5. 3

; P53

←

1

(ii) SKT

PORT3. 0

; P30 = 1?

BR

SETP

SKT

PORT6. 1

; P61 = 1?

BR

SETP

CLR1

PORT5. 3

; P53

←

0

.

.

SETP: SET1 PORT5. 3

; P53

←

1

(5)

Specific address bit manipulation addressing (fmem. bit)

An addressing mode to specify each bit of the input/output port, interrupt, etc. flag, etc. of the peripheral hardware

directly by the instruction’s operand. Consequently, the data memory addresses to which this addressing mode is

applied are FB0H to FBFH, FF0H to FFFH.

While the 1-bit direct addressing mode (mem.bit) is applicable only to the bit set/reset/test instructions, this

addressing mode enables multifarious bit manipulation such as the Boolean operation by the AND1, OR1 and XOR1

instructions, test and reset by the SKTCLR instruction in addition to them.

Example

1.

Test the basic interval timer interrupt request flag (IRQBT) and, if set, clear IRQBT and reset the

P63 pin level.

SKTCLR

IRQBT

; IRQBT = 1?

BR

NO

; NO

CLR1

PORT 6. 3

; YES

2.

If P30 and p61 both 1, reset P53.