NEC PD75402A User Manual

Page 115

104

CHAPTER 5. PERIPHERAL HARDWARE FUNCTIONS

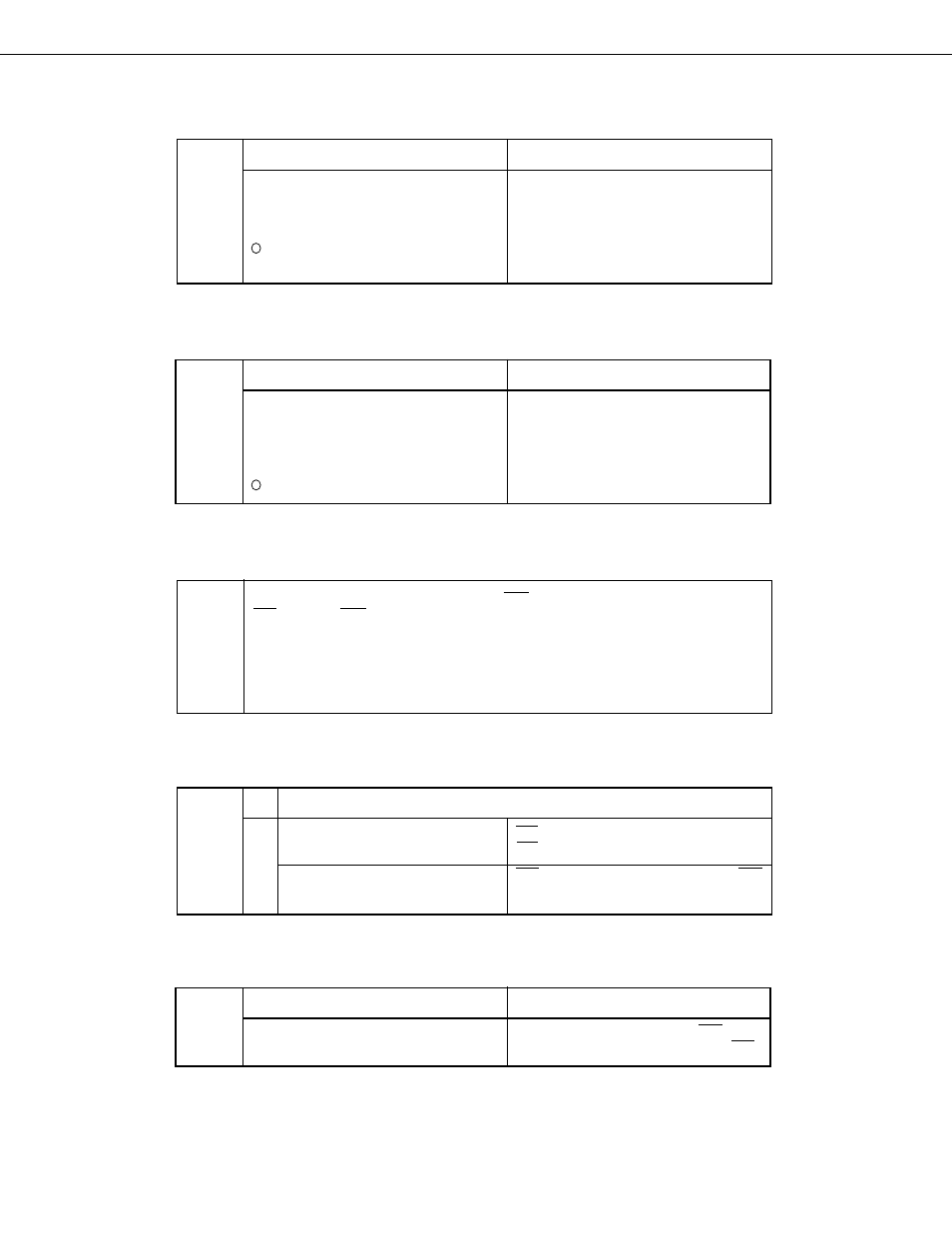

Bus release detection flag (R)

Clearing Conditions (RELD = 0)

Setting Condition (RELD = 1)

➀

When a transfer start instruction is

executed

➁

When RESET is input

➂

When CSIE = 0 (See Fig. 5-25)

When SVA and SIO do not match

when an address is received

RELD

When the bus release signal (REL) is de-

tected

Clearing Conditions (CMDD = 0)

Setting Condition (CMDD = 1)

➀

When a transfer start instruction is

executed

➁

When the bus release signal (REL) is

detected

➂

When RESET is input

When CSIE = 0 (See Fig. 5-25)

CMDD

When the command signal (CMD) is de-

tected

Command detection flag (R)

Acknowledge trigger bit (W)

When ACKT is set after the end of a transfer, ACK is output in synchronization with the next

SCK. After the ACK signal is output, ACKT is automatically cleared (0).

Note 1. ACKT must not be set (1) before completion of a serial tramsfer or during a

transfer.

2. ACKT cannot be clearedby software.

3. When ACKT is set, ACKE should be reset to 0.

Acknowledge enable bit (R/W)

When set before end of transfer

ACK is output is synchronization with the 9th

SCK clock cycle.

When set after end of transfer

ACK is output in synchronization with SCK

immediately after execution of the setting

instruction.

1

Acknowledge detection flag (R)

Clearing Conditions (ACKD = 0)

Setting Condition (ACKD = 1)

➀

When a transfer is started

➁

When RESET is input

ACKD

When the acknowledge signal (ACK) is de-

tected (Synchronized with the rise of SCK)

Disables automatic output of the acknowledge signal (outpt by ACKT is possibel).

0

ACKE

ACKT

4

4