Standby mode setting and operation states – NEC PD75402A User Manual

Page 153

142

CHAPTER 7. STANDBY FUNCTION

7.1

STANDBY MODE SETTING AND OPERATION STATES

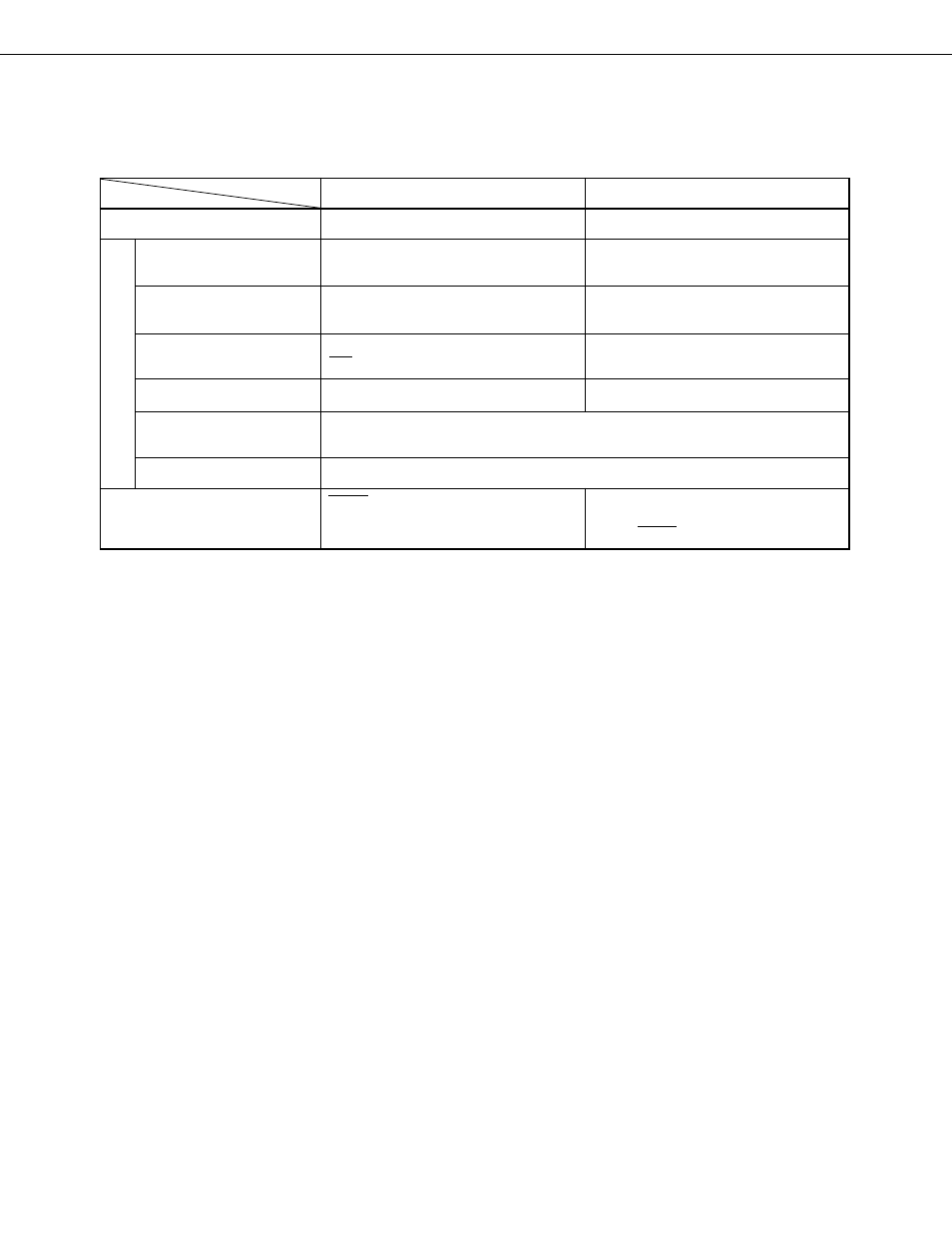

Table 7-1 Standby Mode Operation States

STOP Mode

HALT Mode

Setting instruction

HALT instruction

CPU clock

Φ

only stopped oscillator

(oscillation continues)

Operation

(IRQBT set at basic time interval)

Operation possible

Output other than CPU clock

Φ

possible

Operation state

Operation stopped

INT2 : Operation possible

INT0 : Operation impossible

Interrupt request signal from operable

hardware enabled by interrupt enable

flag or RESET input.

The STOP mode is set by STOP instruction and the HALT mode is set by HALT instruction. (The STOP instruction

and HALT instruction set bits 3 and 2 of the PCC respectively.)

Always write an NOP instruction after the STOP instruction or HALT instruction.

When the CPU operation clock is changed by means of the low-order two bits of the PCC, a time lag may be

generated between rewriting of the PCC and changing of the CPU clock. Therefore, when changing the operating

clock before the standby mode and when changing the CPU clock after standby mode reset, set the standby mode

after the number of machine cycles required to change the CPU clock has elapsed after the PCC is rewritten.

In the standby mode, the data of the general register, flags, mode registers, output latch, and all the other registers

which stop operating in the standby mode and the data memory is retained.

Notes are given below.

Note

1. When the STOP mode is set, the X1 pin is shorted internally to V

SS

(GND potential) to suppress clock

oscillator leakage. Therefore, do not use the STOP mode with systems that use an external clock.

2. STOP mode reset by interrupt request differs as follows for the

µ

PD75402A and the evachip installed

on the evaluation board:

•

µ

PD75402A

••••••

STOP mode not reset by interrupt request.

•

Evachip

••••••••••••••

STOP mode reset by interrupt request.

To eliminate the affect of this difference, disable all interrupt requests before setting the

µ

PD75402A

to the STOP mode.

3. From the standpoint that an interrupt request signal is used to reset the HALT mode, when there is an

interrupt source which sets both the interrupt request flag and interrupt enable flag (1), the HALT mode,

even if entered, is immediately reset.

Reset signal

RESET input

STOP instruction

Clock oscillation stopped

Operation stopped

Operation possible only when external

SCK input selected as serial clock

Operation stopped

Clock generator

Basic interval timer

Serial interface

Clock output circuit

External interrupt

CPU