NEC PD75402A User Manual

Page 67

56

CHAPTER 5. PERIPHERAL HARDWARE FUNCTIONS

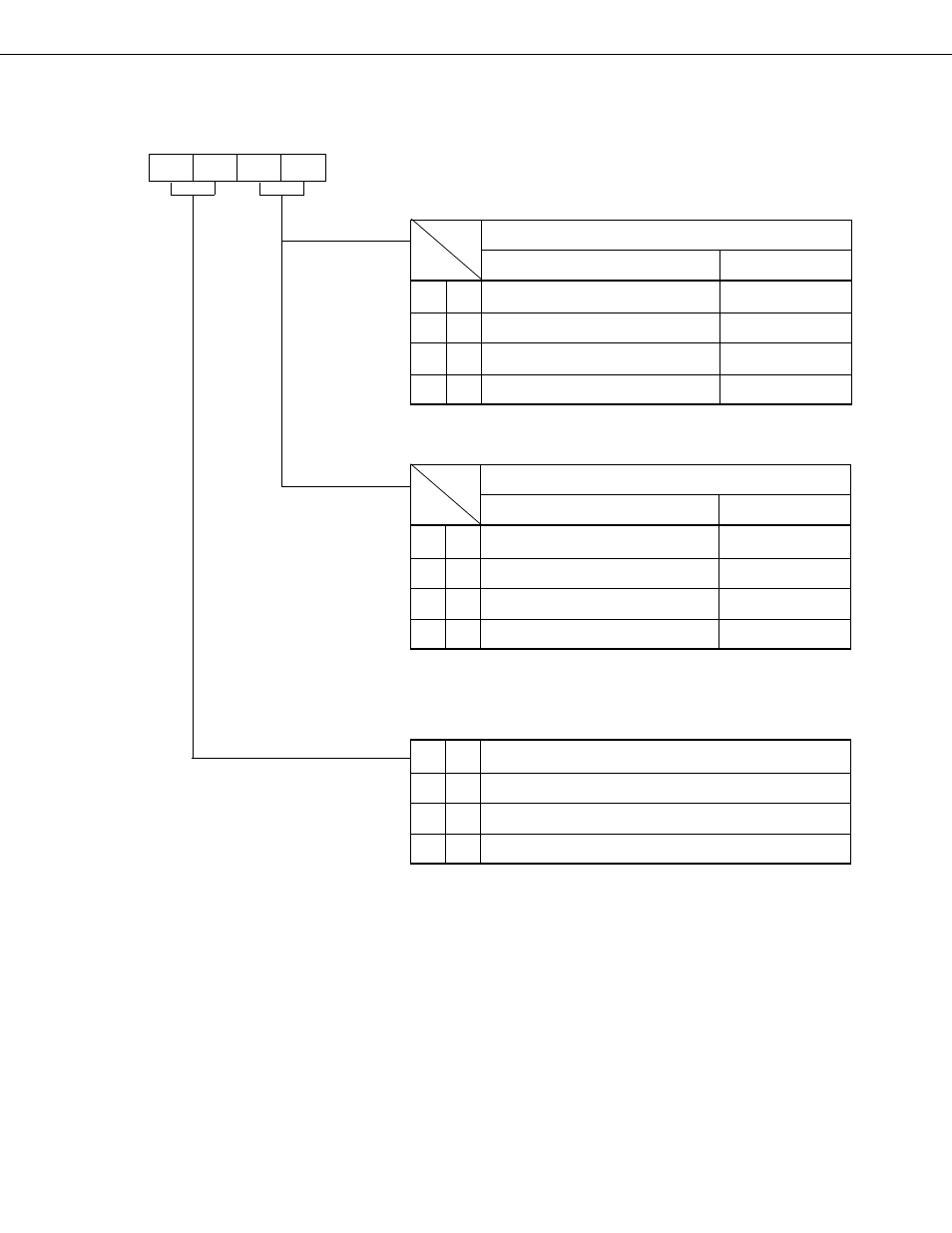

Fig. 5-11 Processor Clock Control Register Format

Note

When using a calue of f

XX

such that 4.19 MHz < f

XX

≤

5.0 MHz, if maximum speed mode :

Φ

f

XX

/4 (PCC1, PCC0

= 11) is set as CPU clock frequency, 1 machine cycle is less than 0.95

µ

s and the standard minimum value

0.95

µ

s is not kept.

Therefore, is this case, PCC1, PCC0 = 11 cannot be set, so it should be used with PCC1, PCC0 = 00 or 10.

As a result, the combination of “f

XX

= 4.19 MHz, PCC1, PCC0 = 11” is maximum speed selection (1 machin

cycle = 0.95

µ

s) as CPU clock.

3

2

1

0

Symbol

FB3H

PCC3

PCC2

PCC1

PCC0

PCC

CPU clock selection bits when f

XX

≤

4.19 MHz

( ) : When f

XX

= 4.19 MHz

CPU Clock Frequency

1 Machine Cycle

0

0

Φ

Output = f

XX

/64 (65.5 kHz)

15.3

µ

s

0

1

Setting prohibited

–

1

0

Φ

= f

XX

/8 (524 kHz)

19.1

µ

s

1

1

Φ

= f

XX

/4 (1.05 MHz)

0.95

µ

s

When 4.19 MHz < f

XX

≤

5.0 MHz

( ) : When f

XX

= 4.19 MHz

CPU Clock Frequency

1 Machine Cycle

0

0

Φ

Output = f

XX

/64 (76.7 kHz)

13

µ

s

0

1

Setting prohibited

–

1

0

Φ

= f

XX

/8 (614 kHz)

1.63

µ

s

1

1

Setting prohibited

–

f

XX

: Main system clock oscillation circuit output frequency

CPU operating mode control bit

Address

0

0

Normal operating mode

0

1

HALT mode

1

0

STOP mode

1

1

Setting prohibited