NEC PD75402A User Manual

Page 101

90

CHAPTER 5. PERIPHERAL HARDWARE FUNCTIONS

(5)

Data transfer order

The

µ

PD75402A 3-wire serial I/O mode differs from that of other 75X series products in that it is not possible to

switch between MSB and LSB as the first bit.

Serial transfer is performed MSB-first.

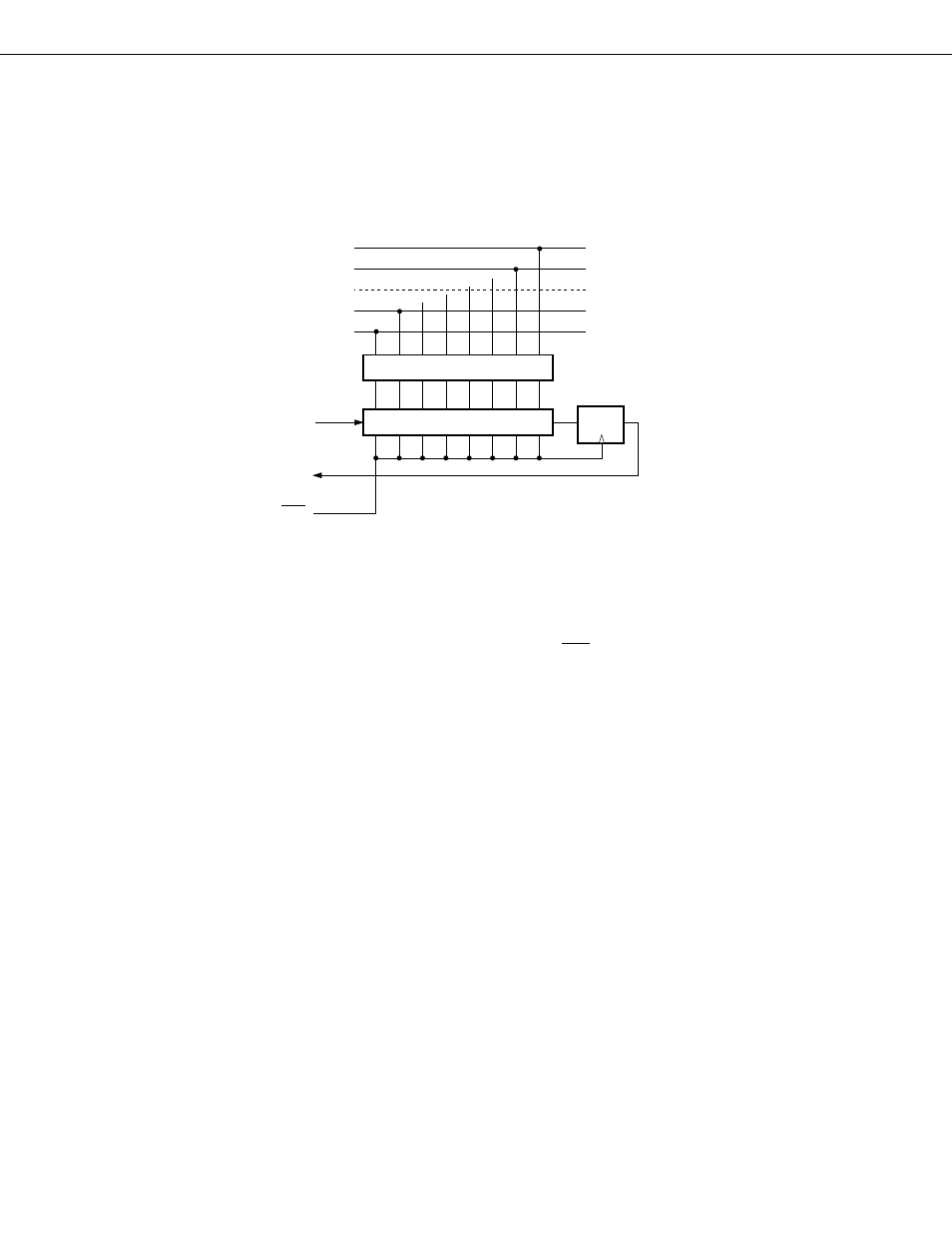

Fig. 5-31 Shift Register (SIO) and Internal Bus Configuration

(6)

Start of transfer

When the following two conditions are met a serial transfer is started by setting transfer data in the shift register

(SIO).

• The serial interface operation enable/disable bit (CSIE) = 1.

• After an 8-bit serial transfer, the internal serial clock is stopped or SCK is high.

Note

The transfer will not be started if CSIE is set to “1” after data is written into the shift register.

When an 8-bit transfer ends, the serial transfer stops automatically and the IRQCSI interrupt request flag is set.

Example

In the following example the data in the RAM specified by the HL register is transferred to SIO, and at

the same time the SIO data is fetched into the accumulator and the serial transfer is started.

MOV

XA, @HL ; Fetch send data from RAM

XCH

XA, SIO ; Exchange send data with receive data and start transfer

7

6

1

0

Internal

Bus

Read/Write Gate

Shift Register (SIO)

SI

SO

SCK

D

Q

SO Latch