NEC PD75402A User Manual

Page 87

76

CHAPTER 5. PERIPHERAL HARDWARE FUNCTIONS

Note

If WUP = 1 is set during BUSY signal output, BUSY is not released. With the SBI, the BUSY signal is output

after the BUSY release directive until the next fall of the serial clock (SCK). When setting WUP = 1, it is

necessary to confirm that the SB0 pin has been driven high after BUSY is released before setting WUP =

1.

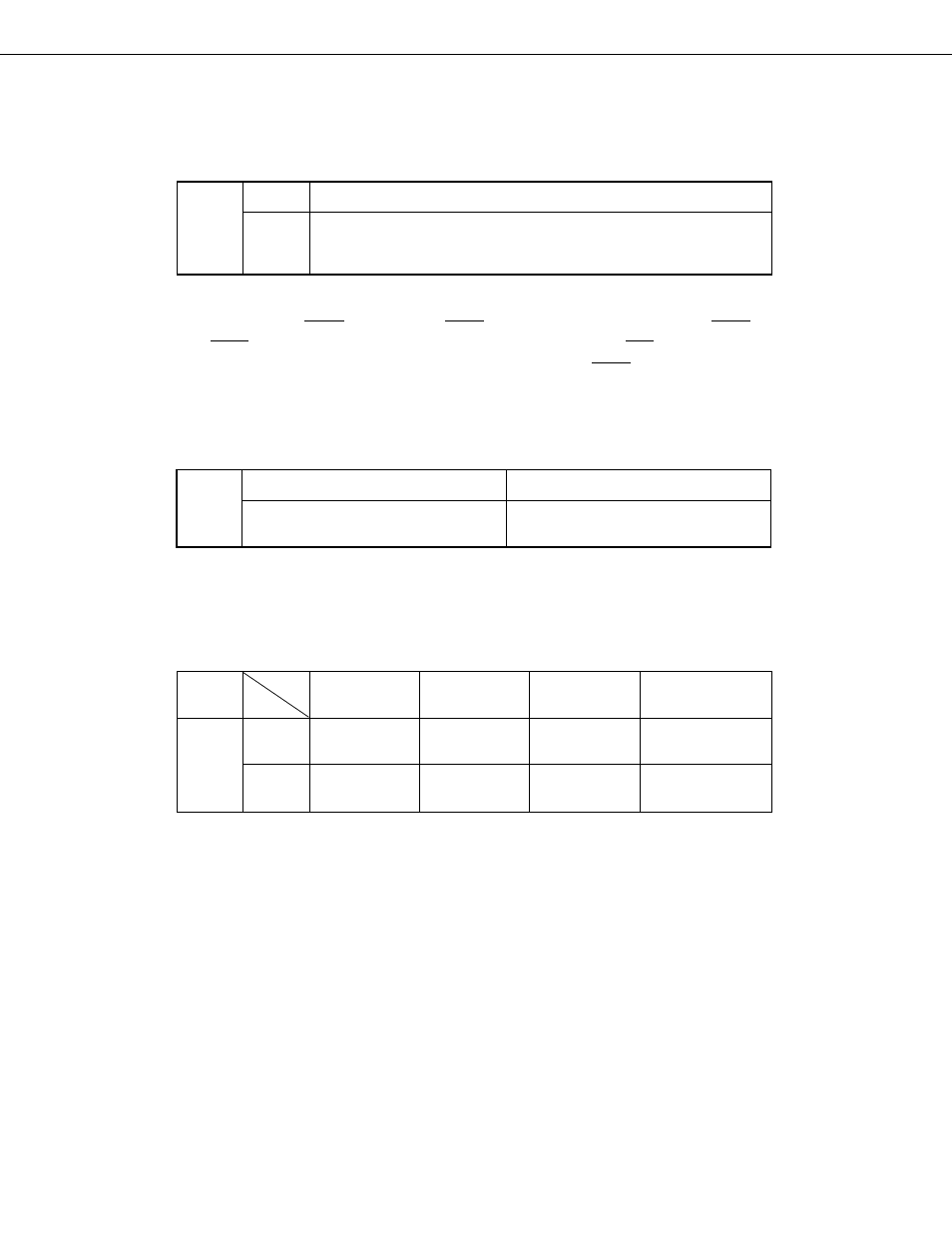

Signal from address comparator (R)

Fig. 5-25 Serial Operating Mode Register (CSIM) Format (2/2)

Wake-up function specification bit (W)

WUP

1

Clearing Condition (COI = 0)

Setting Condition (COI = 1)

When slave address register (SVA) and

shift register data do not match

When slave address register (SVA) and shift

register data match.

COI*

*

A COI read is valid only before the start or after completion of a serial transfer. During a transfer an indeterminate

value will be read. Also, COI data written by an 8-bit manipulation instruction is ignored.

Serial interface operation enable/disable specification bit (W)

0

IRQCSI set at end of every serial transfer in each mode.

Used only in SBI mode. IRQCSI is set only when the address received after bus

release matches the slave address register data (wake-up status). SB0 is high

impedance.

Shift Register

Operation

Serial Clock

Counter

IRQCSI Flag

SO/SB0 & SI Pins

Shift operation

disabled

Cleared

Retained

Port 0 function only

0

CSIE

1

Count operation

Settable

Shift operation

enabled

Function in each

mode plus port 0

function