Arithmetic and logical, Table 9, Block search group – Zilog Z08470 User Manual

Page 59

UM008007-0715

Arithmetic and Logical

Z80 CPU

User Manual

47

Exchange, Block Transfer, and Search Group

The CPIR instruction is merely an extension of the CPl instruction in which the compare is

repeated until either a match is found or the byte counter (register pair BC) becomes zero.

As a result, this single instruction can search the entire memory for any 8-bit character.

The Compare and Decrement (CPD) and Compare, Decrement, and Repeat (CPDR)

instructions are similar; however, their only difference is that they decrement HL after

every compare so that they search the memory in the opposite direction; i.e., the search is

started at the highest location in the memory block.

These block transfer and compare instructions are extremely powerful in string manipula-

tion applications.

Arithmetic and Logical

Table 10 lists all of the 8-bit arithmetic operations that can be performed with the Accu-

mulator. Also listed are the increment (INC) and decrement (DEC) instructions. In all of

these instructions, with the exception of INC and DEC, the specified 8-bit operation is per-

formed between the data in the Accumulator and the source data.

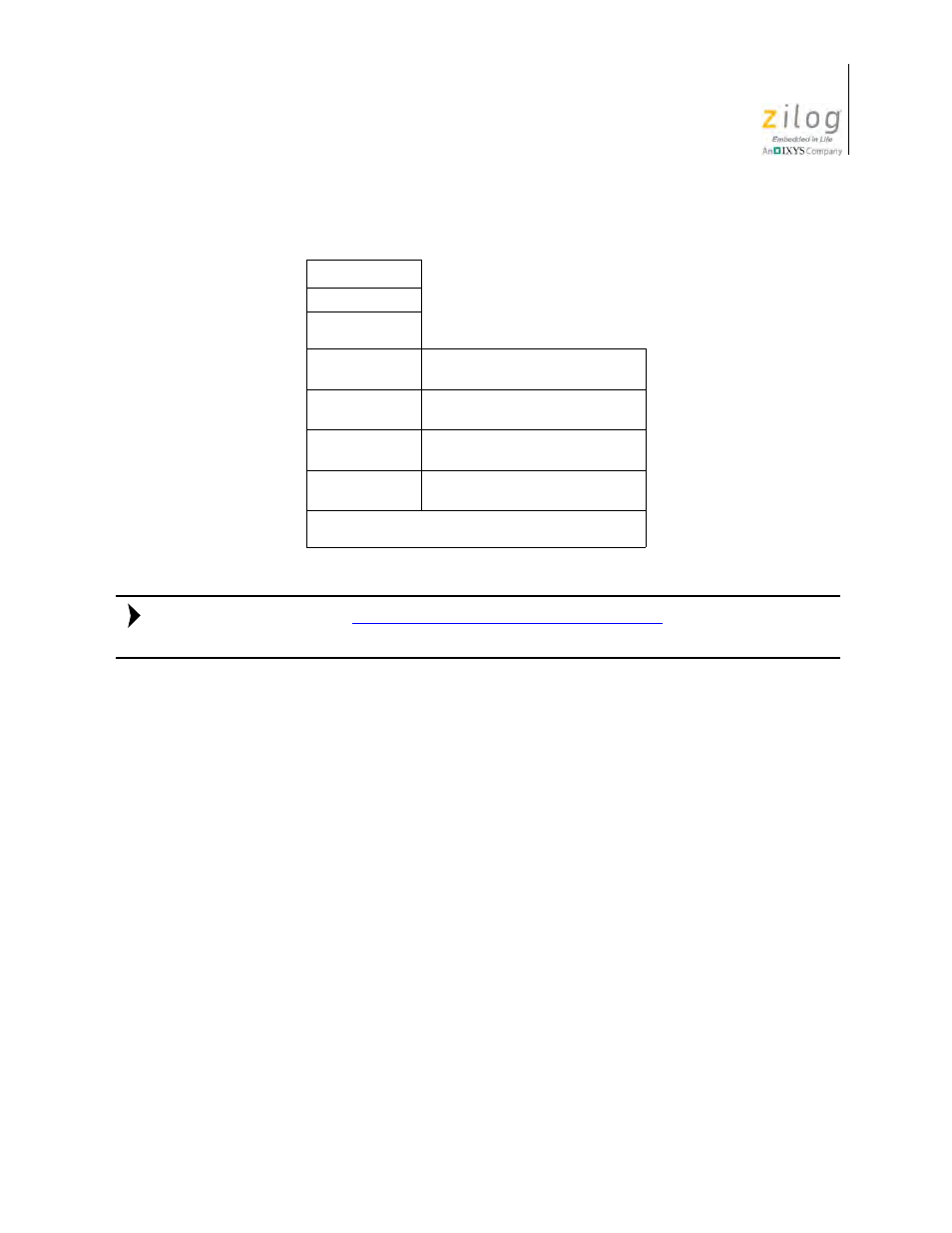

Table 9. Block Search Group

Search Location

Register Indirect

(HL)

(ED)

A1

CPI

Inc HL, Dec BC

(ED)

B1

CPRI. Inc HL, Dec BC

Repeat until) BC = 0 or find match

(ED)

A9

WD Dec HL and BC

(ED)

B9

CPDR Dec HL and BC

Repeat until BC = 0 or find match

Note: HL points to a location in memory to be compared with

Accumulator contents; BC is a byte counter.

Note: