Add a, (iy + d) – Zilog Z08470 User Manual

Page 160

Z80 Instruction Set

UM008007-0715

148

Z80 CPU

User Manual

ADD A, (IY + d)

Operation

A ← A + (IY+d)

Op Code

ADD

Operands

A, (IY + d)

Description

The contents of the Index (register pair IY) Register is added to a two’s complement dis-

placement d to point to an address in memory. The contents of this address is then added to

the contents of the Accumulator, and the result is stored in the Accumulator.

Condition Bits Affected

S is set if result is negative; otherwise, it is reset.

Z is set if result is 0; otherwise, it is reset.

H is set if carry from bit 3: otherwise, it is reset.

P/V is set if overflow; otherwise, it is reset.

N is reset.

C is set if carry from bit 7; otherwise, it is reset.

Example

If the Accumulator contains

11h

, Index Register IY contains

1000h

, and memory location

1005h

contains

22h

, then upon the execution of an ADD A, (IY +

5h

) instruction, the

Accumulator contains

33h

.

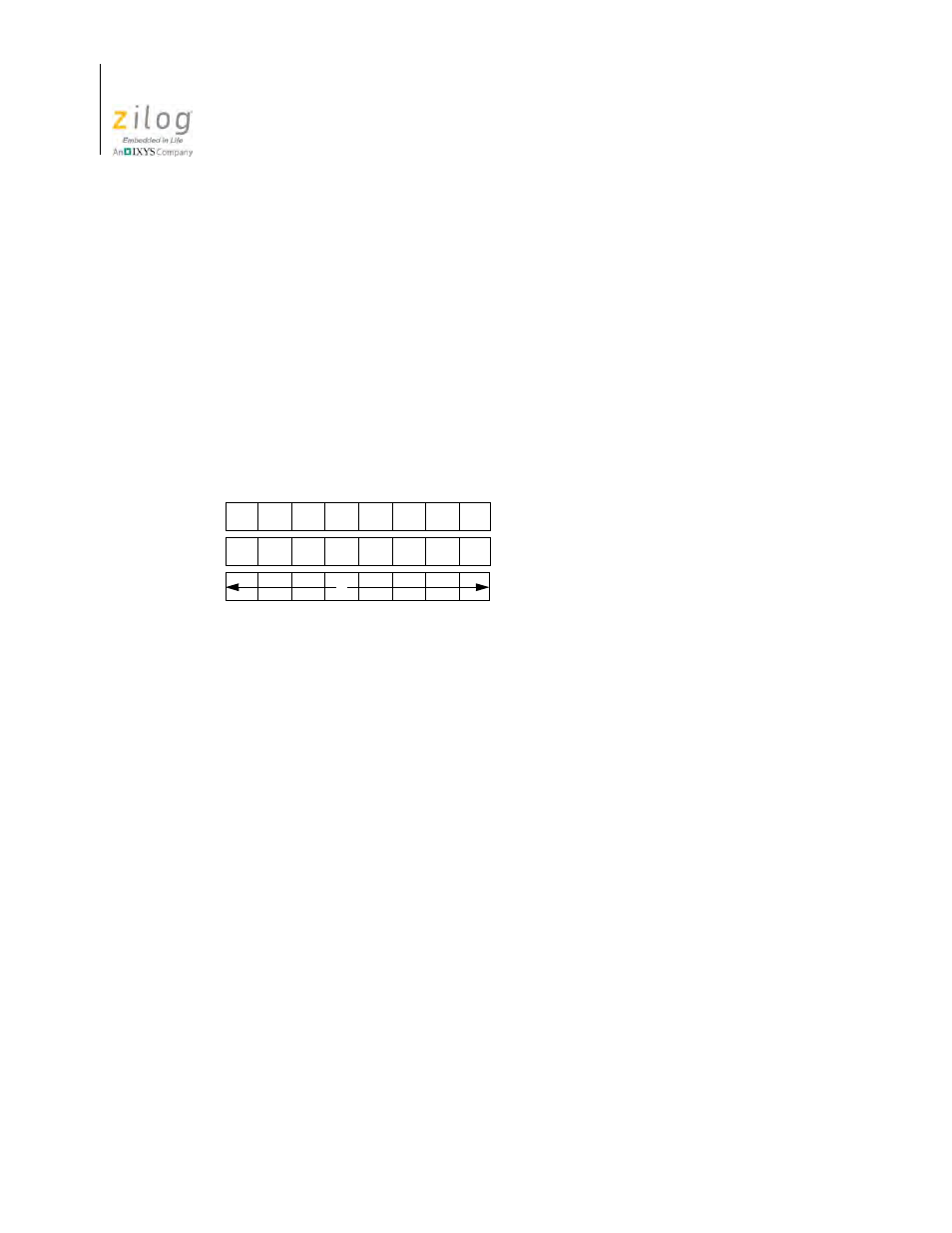

M Cycles

T States

4 MHz E.T.

5

19(4, 4, 3, 5, 3)

4.75

1

1

1

0

1

1

1

1

FD

1

0

0

1

0

1

0

0

86

d