Cpu register, Special-purpose registers, Figure 2 – Zilog Z08470 User Manual

Page 14: Cpu register configuration

Architectural Overview

UM008007-0715

2

Z80 CPU

User Manual

CPU Register

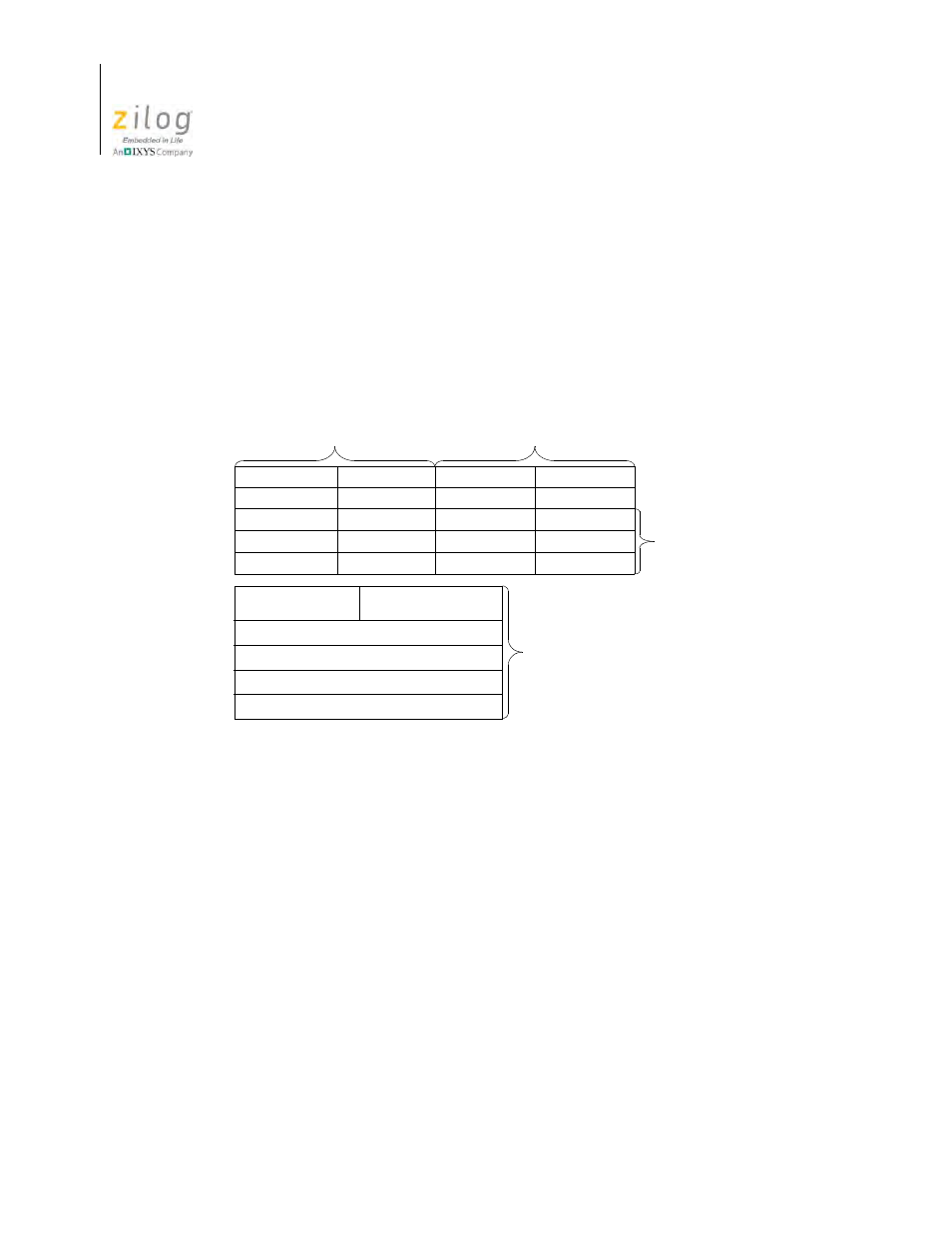

The Z80 CPU contains 208 bits of read/write memory that are available to the program-

mer. Figure 2 shows how this memory is configured to eighteen 8-bit registers and four

16-bit registers. All Z80 CPU’s registers are implemented using static RAM. The registers

include two sets of six general-purpose registers that can be used individually as 8-bit reg-

isters or in pairs as 16-bit registers. There are also two sets of Accumulator and Flag regis-

ters and six special-purpose registers.

Special-Purpose Registers

Program Counter (PC).

The program counter holds the 16-bit address of the current

instruction being fetched from memory. The Program Counter is automatically incre-

mented after its contents are transferred to the address lines. When a program jump occurs,

the new value is automatically placed in the Program Counter, overriding the incrementer.

Stack Pointer (SP).

The stack pointer holds the 16-bit address of the current top of a stack

located anywhere in external system RAM memory. The external stack memory is orga-

nized as a last-in first-out (LIFO) file. Data can be pushed onto the stack from specific

CPU registers or popped off of the stack to specific CPU registers through the execution of

PUSH and POP instructions. The data popped from the stack is always the most recent

data pushed onto it. The stack allows simple implementation of multiple level interrupts,

unlimited subroutine nesting and simplification of many types of data manipulation.

Figure 2. CPU Register Configuration

General

Purpose

Registers

Accumulator

H '

Special

Purpose

Registers

Index Register

Index Register

Stack Pointer

Program Counter

Interrupt Vector

I

H

L

L '

D

E

D '

E '

B

C

B '

B '

A

F

A '

F '

Flags

Accumulator

Flags

Alternate Register Set

Main Register Set

Memory Refresh

R

IX

IY

SP

PC