Sbc hl, ss – Zilog Z08470 User Manual

Page 202

Z80 Instruction Set

UM008007-0715

190

Z80 CPU

User Manual

SBC HL, ss

Operation

HL ← HI – ss – CY

Op Code

SBC

Operands

HL, ss

Description

The contents of the register pair ss (any of register pairs BC, DE, HL, or SP) and the Carry

Flag (C flag in the F Register) are subtracted from the contents of register pair HL, and the

result is stored in HL. In the assembled object code, operand ss is specified as follows:

Condition Bits Affected

S is set if result is negative; otherwise, it is reset.

Z is set if result is 0; otherwise, it is reset.

H is set if borrow from bit 12; otherwise, it is reset.

P/V is set if overflow; otherwise, it is reset.

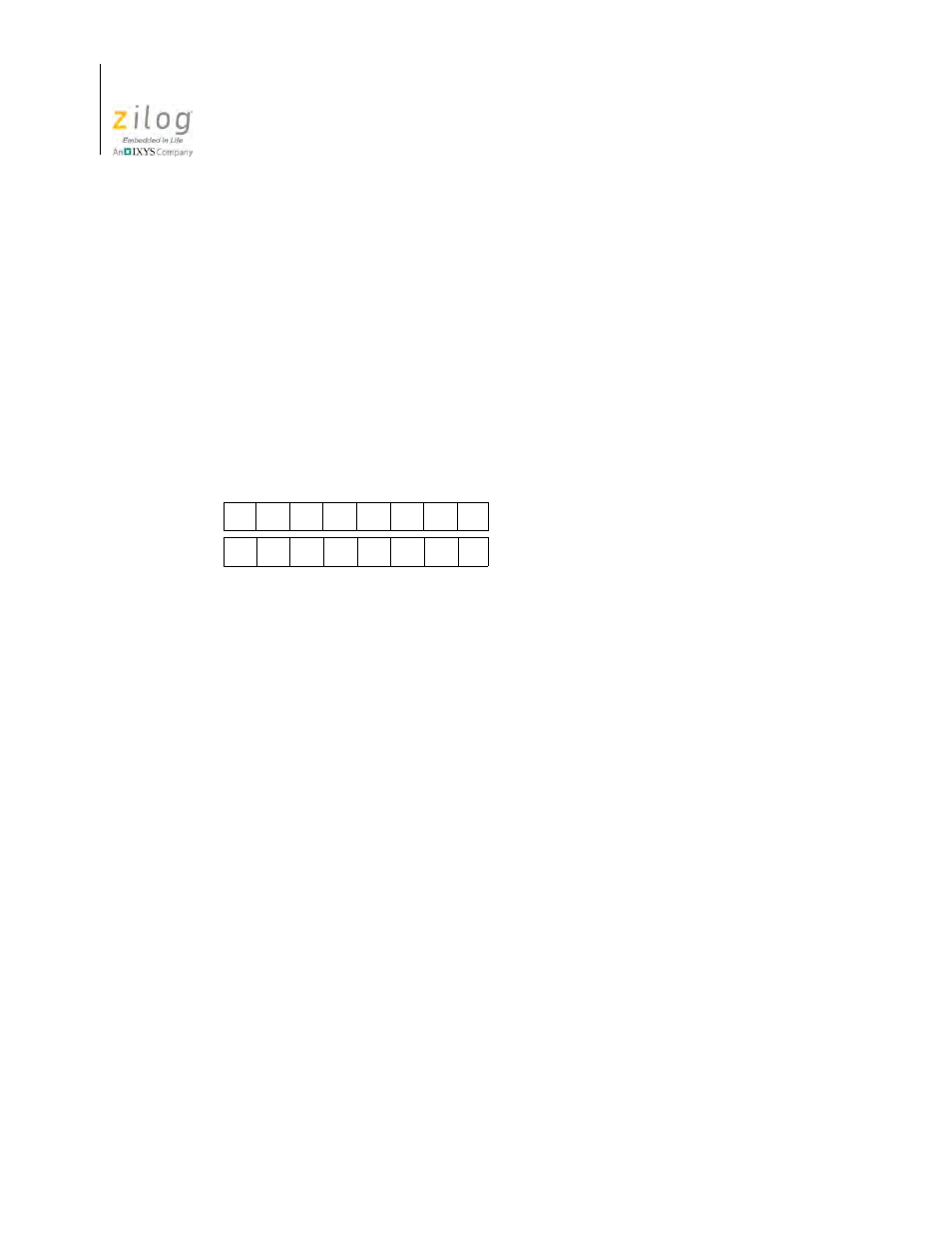

Register

Pair

ss

BC

00

DE

01

HL

10

SP

11

M Cycles

T States

4 MHz E.T.

4

15 (4, 4, 4, 3)

3.75

1

1

0

0

1

1

1

1

ED

0

1

s

1

0

0

s

0