Zilog Z16F2810 User Manual

Page 98

CLR Instruction

UM018809-0611

82

ZNEO

®

CPU Core

User Manual

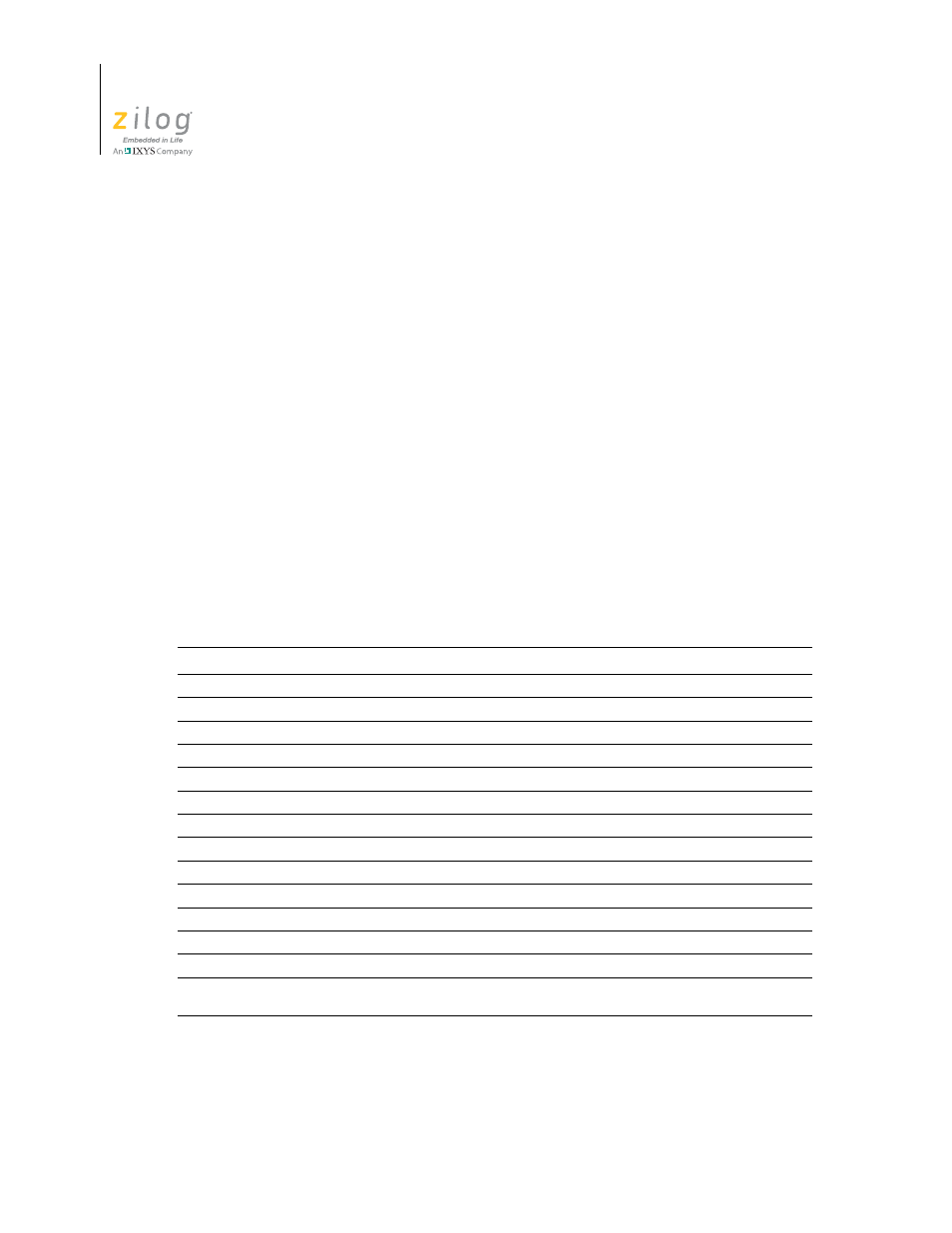

CLR

Definition

Clear

Syntax

CLR dst

Operation

dst

0

Description

All bits of the destination operand are cleared to

0

.

Flags

Flags are not affected by this instruction.

Syntax and Opcodes

Instruction, Operands

Word 0

Word 1

Word 2

CLR Rd

{3H, Rd, 00H}

1

CLR addr16

{ADAH, 1x00B}

addr16

CLR addr32

{ADBH, 1x00B}

addr[31:16]

addr[15:0]

CLR (Rd)

{ACH, 1x00B, Rd}

CLR soff14(Rd)

{ADCH, Rd}

{1xB, soff14}

CLR.W addr16

ADA4H

addr16

CLR.W addr32

ADB4H

addr[31:16]

addr[15:0]

CLR.W (Rd)

{AC4H, Rd}

CLR.W soff14(Rd)

{ADCH, Rd}

{01B, soff14}

CLR.B addr16

ADA0H

addr16

CLR.B addr32

ADB0H

addr[31:16]

addr[15:0]

CLR.B (Rd)

{AC0H, Rd}

CLR.B soff14(Rd)

{ADCH, Rd}

{00B, soff14}

Note:

1. The ZNEO CPU assembler uses an LD opcode to implement CLR Rd.