Zilog Z16F2810 User Manual

Page 75

UM018809-0611

Instruction Opcodes

ZNEO

®

CPU Core

User Manual

59

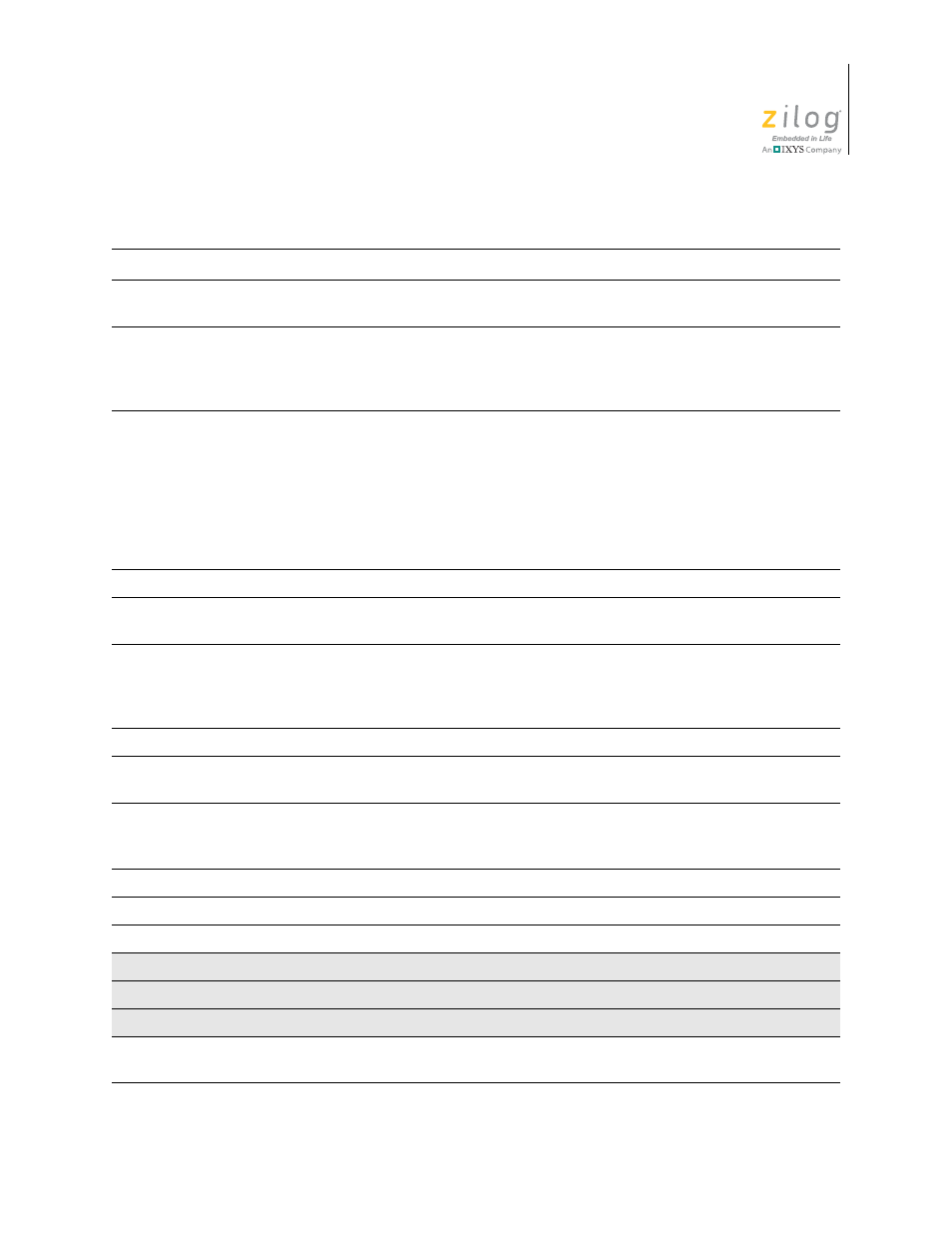

0001 001+ ssss dddd

LD Rd, (Rs)

LD Rd, (Rs++)

Load dst register from Quad with optional

Postincrement.

0001 01b+ ssss dddd

LD.B (--Rd), Rs

LD.B (Rd++), Rs

LD.W (--Rd), Rs

LD.W (Rd++), Rs

Store register to Byte or Word with Predecre-

ment/Postincrement.

0001 1zb+ ssss dddd

LD.UB Rd, (Rs)

LD.SB Rd, (Rs)

LD.UB Rd, (Rs++)

LD.SB Rd, (Rs++)

LD.UW Rd, (Rs)

LD.SW Rd, (Rs)

LD.UW Rd, (Rs++)

LD.SW Rd, (Rs++)

Load dst register from Byte or Word with

optional Postincrement and Unsigned/Signed

extension.

0010 dddd ssss ssss

ADD Rd, Rs1+Rs2

Add using two src registers, one dst.

0011 dddd iiii iiii

LD Rd, #simm8

Load dst register from immediate 8 bits with

Signed extension.

0100 00zb ssss dddd

EXT.UB Rd, Rs

EXT.SB Rd, Rs

EXT.UW Rd, Rs

EXT.SW Rd, Rs

Load 8 or 16 bits to dst from src register with

Unsigned/Signed extension.

0100 0100 ssss dddd

LD Rd, Rs

Load dst from src register.

0100 0101 000z dddd

iiii iiii iiii iiii

LD Rd, #simm17

Load dst register from immediate 16 bits plus

sign bit z; Signed extension.

0100 0101 0010 dddd

iiii iiii iiii iiii

iiii iiii iiii iiii

LD Rd,#imm32

Load dst register from immediate 32 bits.

0100 0101 0011 dddd

LDES Rd

Fill dst from Sign bit.

0100 0101 0100 dddd

COM Rd

Complement destination.

0100 0101 0101 dddd

NEG Rd

Negate dst (subtract from zero).

0100 0101 011x xxxx

—

Unimplemented

0100 0101 1xxx xxxx

—

Unimplemented

0100 011x xxxx xxxx

—

Unimplemented

0100 1000 ssss dddd

0xrr rrrr rrrr rrrr

LD Rd, soff14(Rs)

Load dst from Quad pointed to by src plus

signed offset.

Table 18. ZNEO CPU Instructions Listed by Opcode (Continued)

Opcode Format

Instruction, Operands

Description