Zilog Z16F2810 User Manual

Page 186

SUB Instruction

UM018809-0611

170

ZNEO

®

CPU Core

User Manual

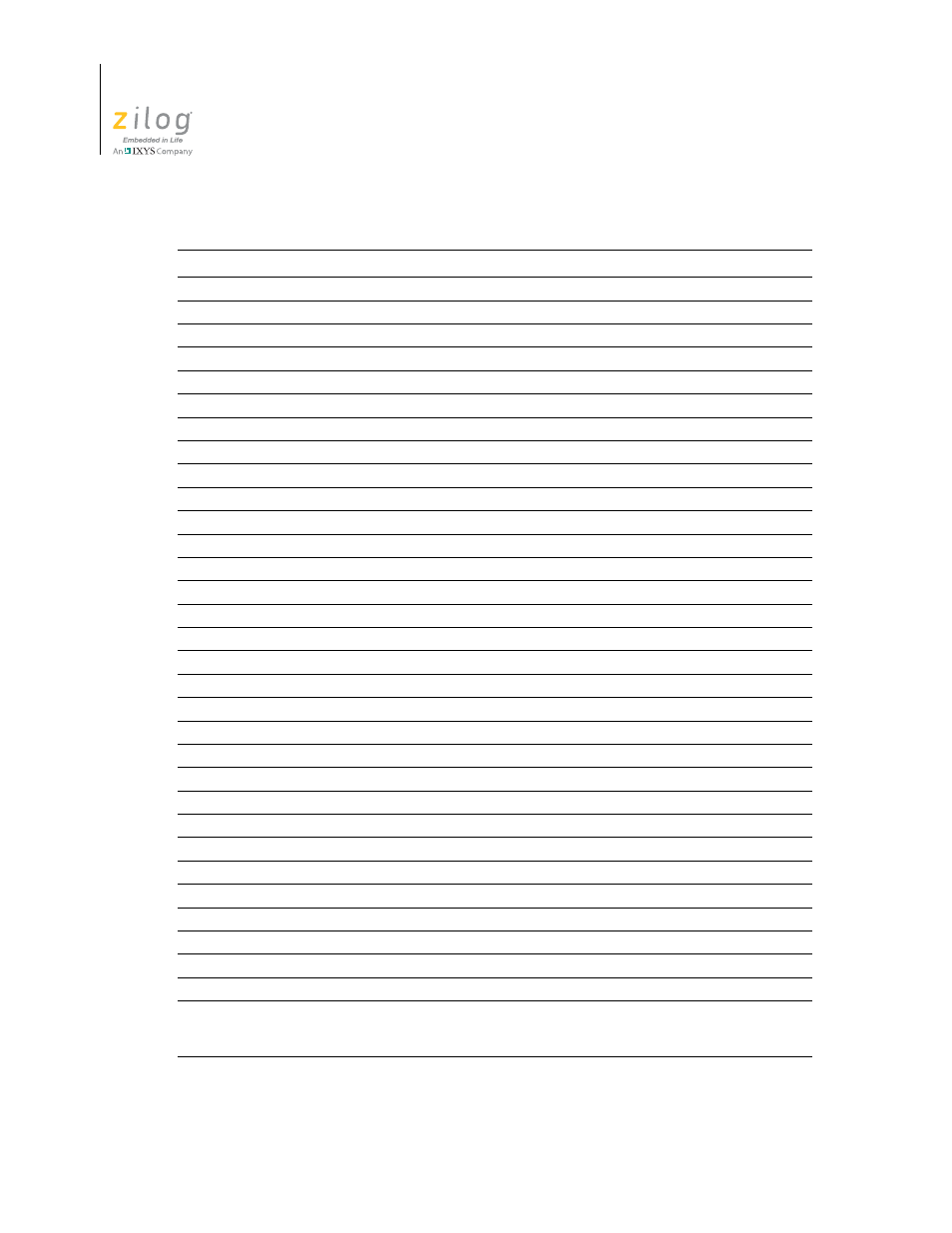

Syntax and Opcodes

Instruction, Operands

Word 0

Word 1

Word 2

SUB Rd, #imm32

{AA9H, Rd}

imm[31:16]

imm[15:0]

SUB Rd, #uimm16

1

{AA1H, Rd}

uimm16

SUB Rd, Rs

{A1H, Rs, Rd}

SUB Rd, addr16

{714H, Rd}

addr16

SUB Rd, addr32

{71CH, Rd}

addr[31:16]

addr[15:0]

SUB Rd, soff13(Rs)

{79H, Rs, Rd}

{100B, soff13}

SUB addr16, Rs

{717H, Rs}

addr16

SUB addr32, Rs

{71FH, Rs}

addr[31:16]

addr[15:0]

SUB (Rd), #imm32

{AB9H, Rd}

imm[31:16]

imm[15:0]

SUB (Rd), #simm16

{AD1H, Rd}

simm16

SUB soff13(Rd), Rs

{79H, Rs, Rd}

{111B, soff13}

SUB.W addr16, Rs

{716H, Rs}

addr16

SUB.W addr32, Rs

{71EH, Rs}

addr[31:16]

addr[15:0]

SUB.W (Rd), #imm16

{AB1H, Rd}

imm16

SUB.W soff13(Rd), Rs

{79H, Rs, Rd}

{110B, soff13}

SUB.SW Rd, addr16

{713H, Rd}

addr16

SUB.SW Rd, addr32

{71BH, Rd}

addr[31:16]

addr[15:0]

SUB.SW Rd, soff13(Rs)

{79H, Rs, Rd}

{011B, soff13}

SUB.UW Rd, addr16

{712H, Rd}

addr16

SUB.UW Rd, addr32

{71AH, Rd}

addr[31:16]

addr[15:0]

SUB.UW Rd, soff13(Rs)

{79H, Rs, Rd}

{010B, soff13}

SUB.B addr16, Rs

{715H, Rs}

addr16

SUB.B addr32, Rs

{71DH, Rs}

addr[31:16]

addr[15:0]

SUB.B (Rd), #imm8

{AD9H, Rd}

{xH, x001B, imm8}

SUB.B soff13(Rd), Rs

{79H, Rs, Rd}

{101B, soff13}

SUB.SB Rd, addr16

{711H, Rd}

addr16

SUB.SB Rd, addr32

{719H, Rd}

addr[31:16]

addr[15:0]

SUB.SB Rd, soff13(Rs)

{79H, Rs, Rd}

{001B, soff13}

SUB.UB Rd, addr16

{710H, Rd}

addr16

SUB.UB Rd, addr32

{718H, Rd}

addr[31:16]

addr[15:0]

SUB.UB Rd, soff13(Rs)

{79H, Rs, Rd}

{000B, soff13}

Note:

1. The one-word instruction

ADD Rd, #–simm8

can be used for 8-bit immediate-to-register sub-

traction if ADD Flags behavior is acceptable.