Table 17, Operand symbols, Table 18 – Zilog Z16F2810 User Manual

Page 72: Zneo cpu instructions listed by opcode, Table 17 lis

Instruction Opcodes

UM018809-0611

56

ZNEO

®

CPU Core

User Manual

Table 18 lists instructions by opcode. Unimplemented opcodes are shaded in grey.

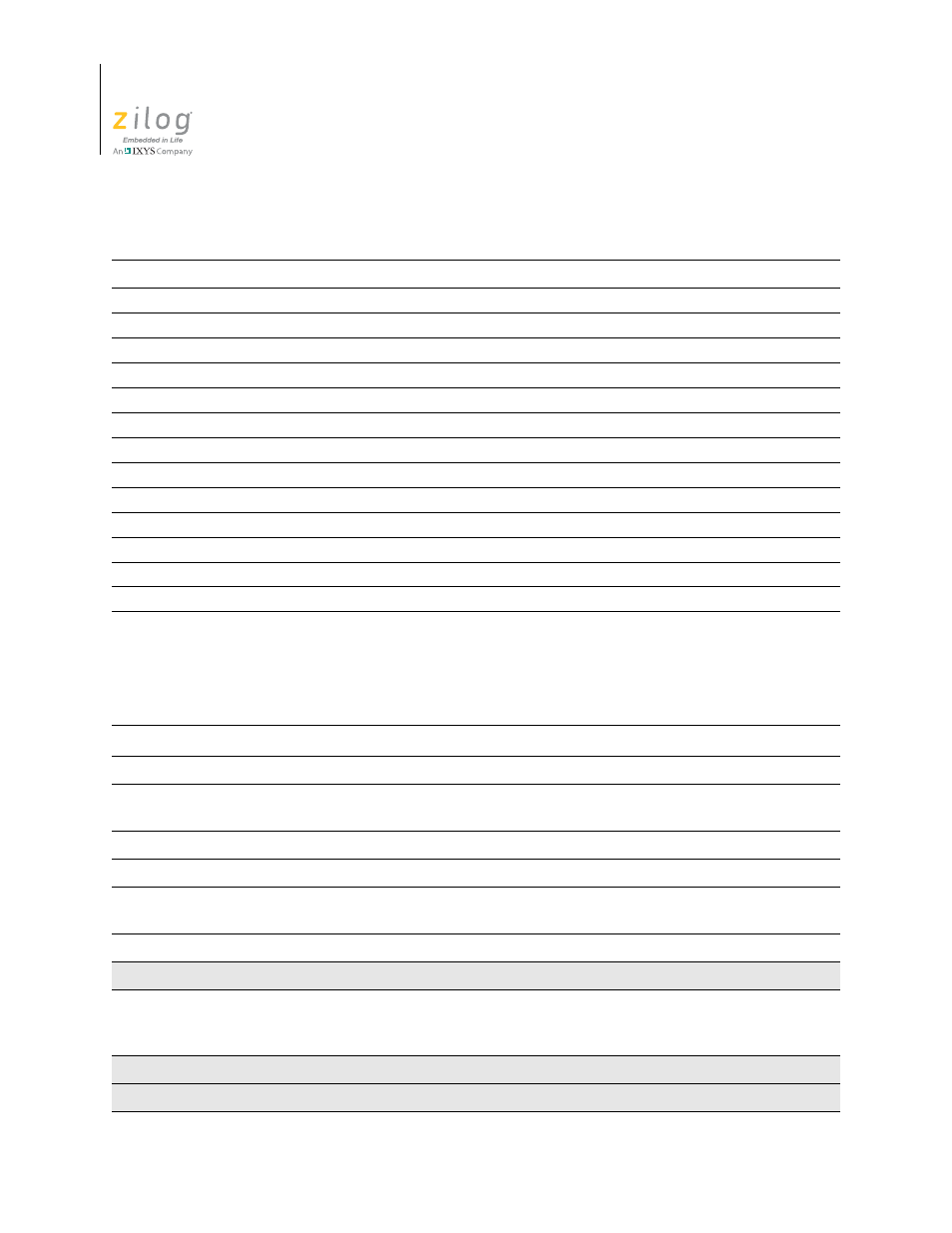

Table 17. Operand Symbols

Operand Abbreviation

Meaning

addr16, addr32

16- or 32-bit direct address.

cc4

4-bit condition code.

imm32

Immediate destination-sized operand with the specified number of bits.

uimm8

Unsigned immediate short operand with the specified number of bits.

simm16

Signed immediate short operand with the specified number of bits.

mask

Register mask (list of ALU registers).

vector8

8-bit vector number.

Rs

Source register name.

Rd

Destination register name.

src

Source operand.

dst

Destination operand.

soff14, soff13, soff6

Signed indirect address (pointer) offset.

rel

Relative jump offset.

Table 18. ZNEO CPU Instructions Listed by Opcode

Opcode Format

Instruction, Operands

Description

0000 0000 0000 0000

BRK

Debugger Break.

0000 0000 0000 0001

UNLINK

Unlink Frame

(LD R15, R14; POP R14).

0000 0000 0000 0010

PUSHF

Push Flags Register .

0000 0000 0000 0011

POPF

Pop Flags Register.

0000 0000 0000 0100

ATM

Disable Interrupts and DMA during next three

instructions.

0000 0000 0000 0101

NOFLAGS

Disable write to FLAGS on next instruction.

0000 0000 0000 0110

—

Unimplemented

0000 0000 0000 0111

—

Extend prefix used to select extended function

for next ADD, SUB, CP, CPZ, SRR, SRA, SLL,

or UDIV instruction.

0000 0000 0000 1xxx

—

Unimplemented

0000 0000 0001 xxxx

—

Unimplemented