Endianness, Bus widths, Endianness bus widths – Zilog Z16F2810 User Manual

Page 35: Figure 4, Endianness of words and quads

UM018809-0611

Address Space

ZNEO

®

CPU Core

User Manual

19

Endianness

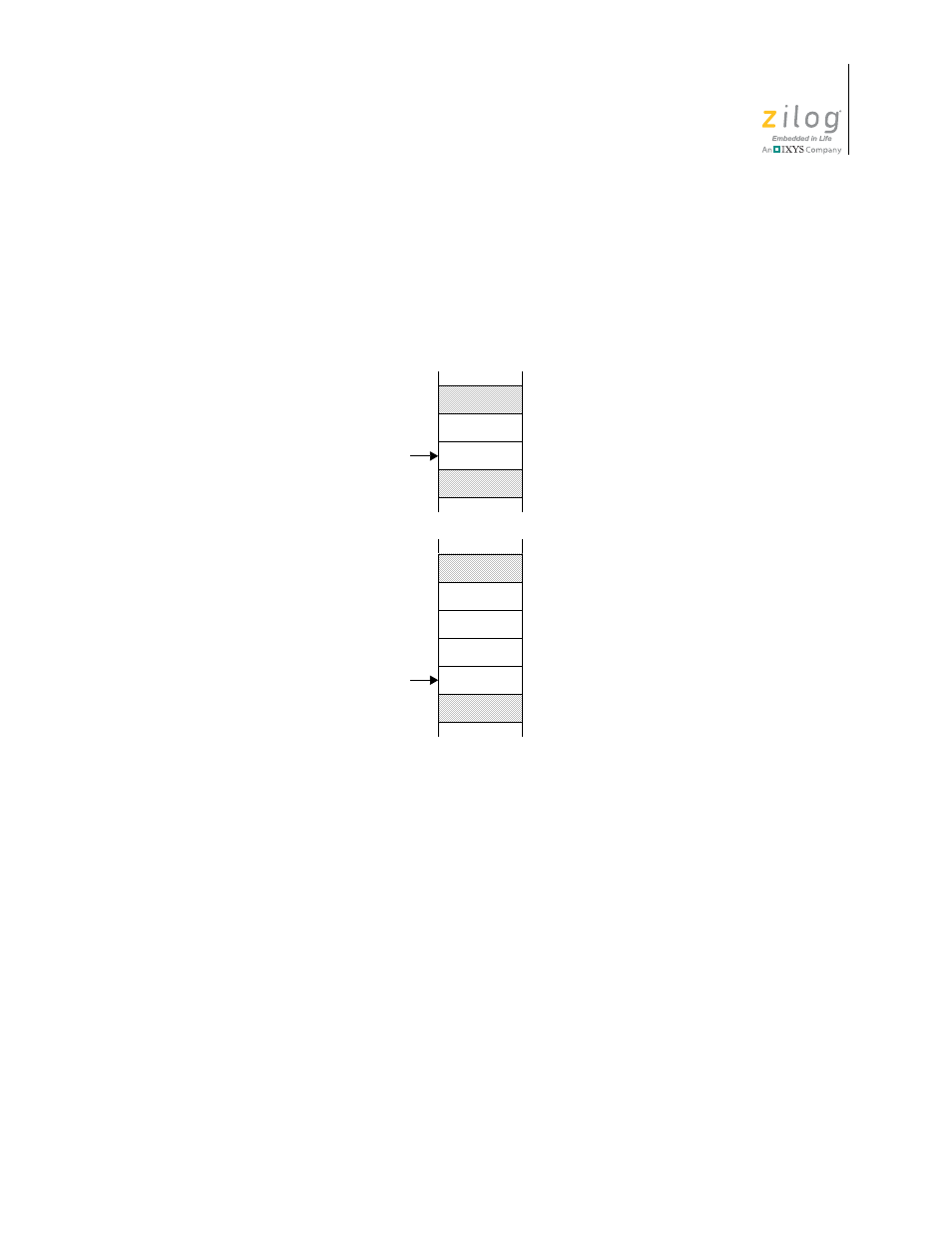

The ZNEO CPU accesses data in Big Endian order; which means the address of a multi-

byte Word or Quad points to the most significant byte (MSB). Figure 4 displays the Endi-

anness of the ZNEO CPU.

Bus Widths

The ZNEO CPU can access 8-bit or 16-bit wide memories. The data buses of the internal

nonvolatile memory and internal RAM are 16-bits wide. The internal peripherals are a mix

of 8-bit and 16-bit peripherals. The external memory bus can be configured as an 8-bit or

16-bit memory bus.

If a 16-bit or 32-bit operation is performed on a 16-bit wide memory, the number of mem-

ory accesses depends on the alignment of the address. If the address is even, a 16-bit oper-

ation takes one memory access and a 32-bit operation takes two memory accesses. If the

address is odd (unaligned), a 16-bit operation takes two memory accesses and a 32-bit

operation takes three memory accesses. Figure 5 displays this behavior for 16-bit and 32-

bit access.

Figure 4. Endianness of Words and Quads

FF_0080H

FF_0081H

FF_0082H

FF_0083H

MSB

LSB

Address

of Quad

FF_0080H

FF_0081H

MSB

LSB

Address

of Word