Cpu control register (cpuctl), Table 4, Cpu control register – Zilog Z16F2810 User Manual

Page 29

UM018809-0611

Architectural Overview

ZNEO

®

CPU Core

User Manual

13

CPU Control Register (CPUCTL)

Bits [1:0] of the CPU Control Register

on page 13) control access to the

ZNEO CPU buses through DMA bandwidth selection.

For more details about the available peripheral control and data registers, and additional

information about DMA operation, refer to the device specific Product Specification.

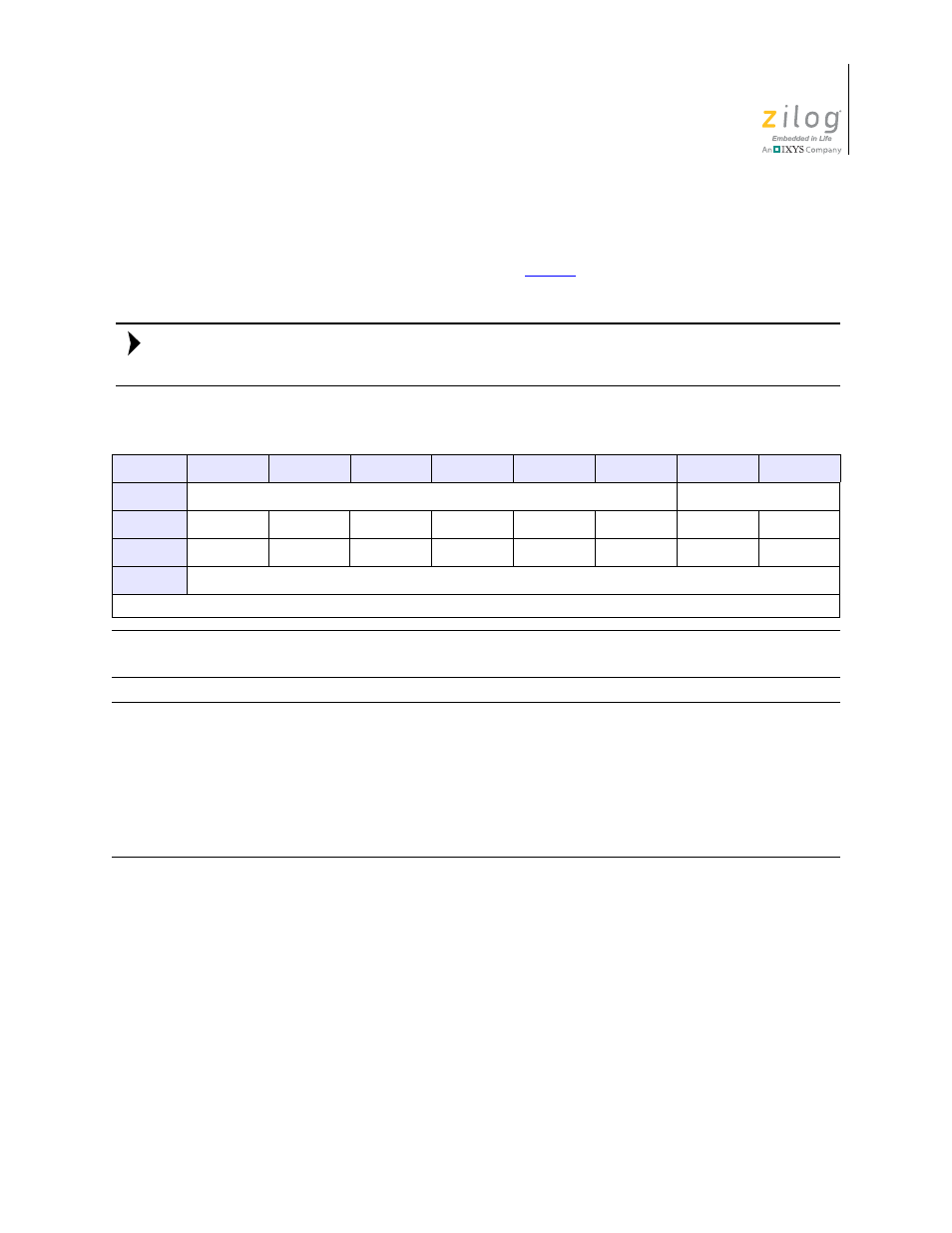

Table 4. CPU Control Register

Bit

7

6

5

4

3

2

1

0

Field

Reserved

DMABW

Reset

1

1

1

1

1

1

1

1

R/W

R

R

R

R

R

R

R/W

R/W

Address

FFFF_E012H

Note: R = Read-only; R/W = Read/Write; R/W0 = Read/Write to 0.

Bit

Position Description

[7:2]

Reserved; must be zero.

[1:0]

DMA Bandwidth Selection (DMABW)

The ZNEO CPU can be configured to support four levels of Direct Memory Access (DMA) Con-

troller bus bandwidth. Write one of the following values to DMABW[1:0] to select the portion of

bus bandwidth allocated to DMA operations:

00 = DMA can consume 100% of the bus bandwidth

01 = DMA is allowed one transaction for each CPU operation

10 = DMA is allowed one transaction for every two CPU operations

11 = DMA is allowed one transaction for every three CPU operations

Note: