Revision history – Zilog Z16F2810 User Manual

Page 3

UM018809-0611

Revision History

ZNEO

®

CPU Core

User Manual

iii

Revision History

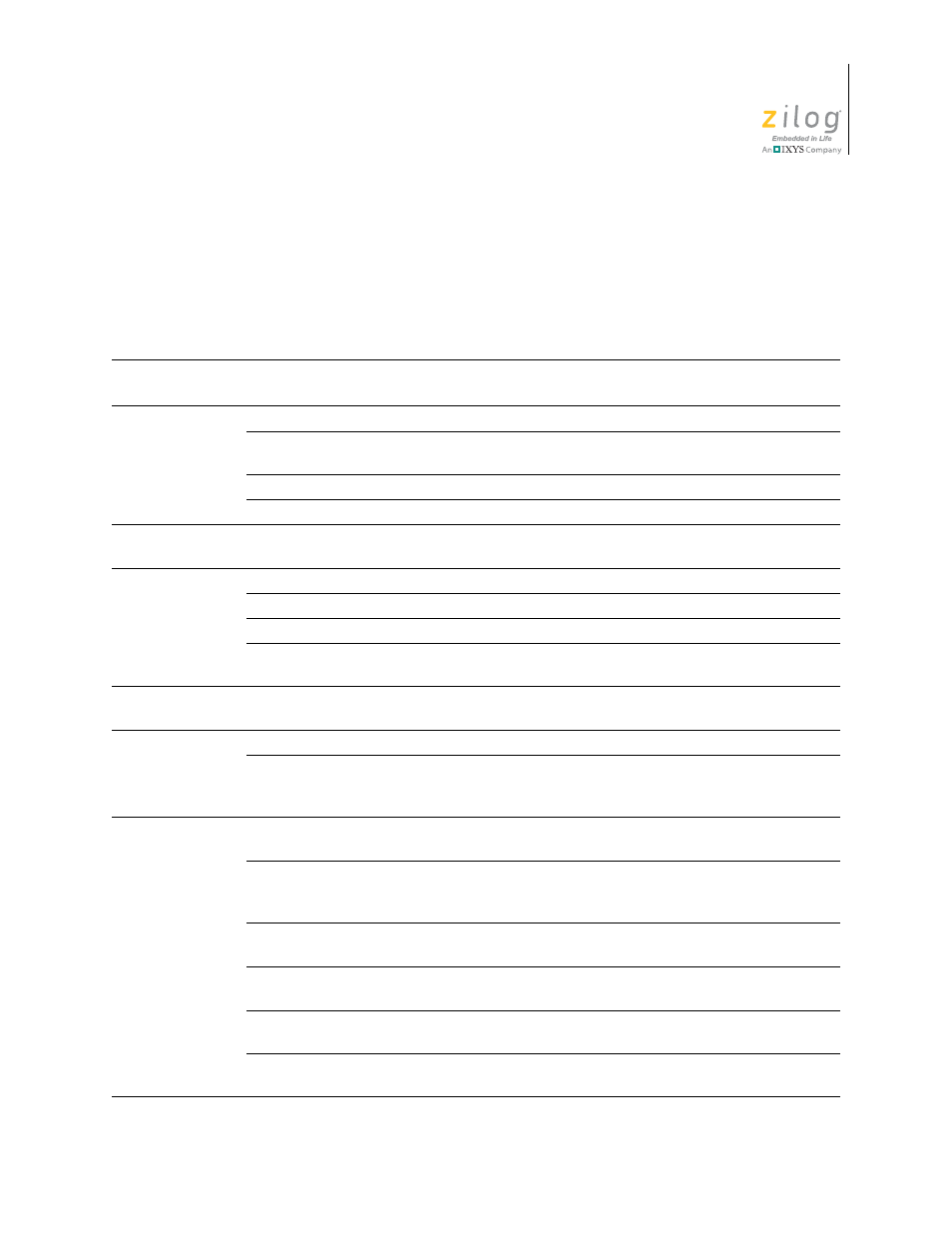

Each instance in the Revision History table below reflects a change to this document from

its previous version. For more details, click the appropriate links in the table.

Date

Revision

Level

Section

Description

Page

May

2011

09

All

Updated for style.

All

Using the Program Counter as

a Base Address

Added note.

Added addressing mode offset description.

Corrected After address in Example.

Aug

2010

08

Updated Syntax and Opcodes table.

Feb

2008

07

Updated User Flag description.

Updated example.

Updated first paragraph.

Updated second step for Stack Overflow

protection.

Sep

2007

06

Updated Examples for DEC Instruction.

Mar

2007

05

Change in instruction.

Flags Register (FLAGS), Vec-

tored Interrupts, Instruction Set

Reference

Updated with CIRQE bit.

May

2006

04

Multiple

Updated ZNEO trademark issues. Applied

current publications template.

All

Features, Control Registers,

Address Space, I/O Memory,

Direct Memory Addressing

Clarified size of address space.

,

Clarified section.

Memory Map, Jump Addressing Jump addresses FF_E000H and above

are reserved.

Internal Nonvolatile Memory,

Internal RAM

Clarified use of assembler address

ranges.

16-bit address range is in highest and low-

est 32K blocks, not 8K blocks.