Zilog Z16F2810 User Manual

Page 132

LD Instruction

UM018809-0611

116

ZNEO

®

CPU Core

User Manual

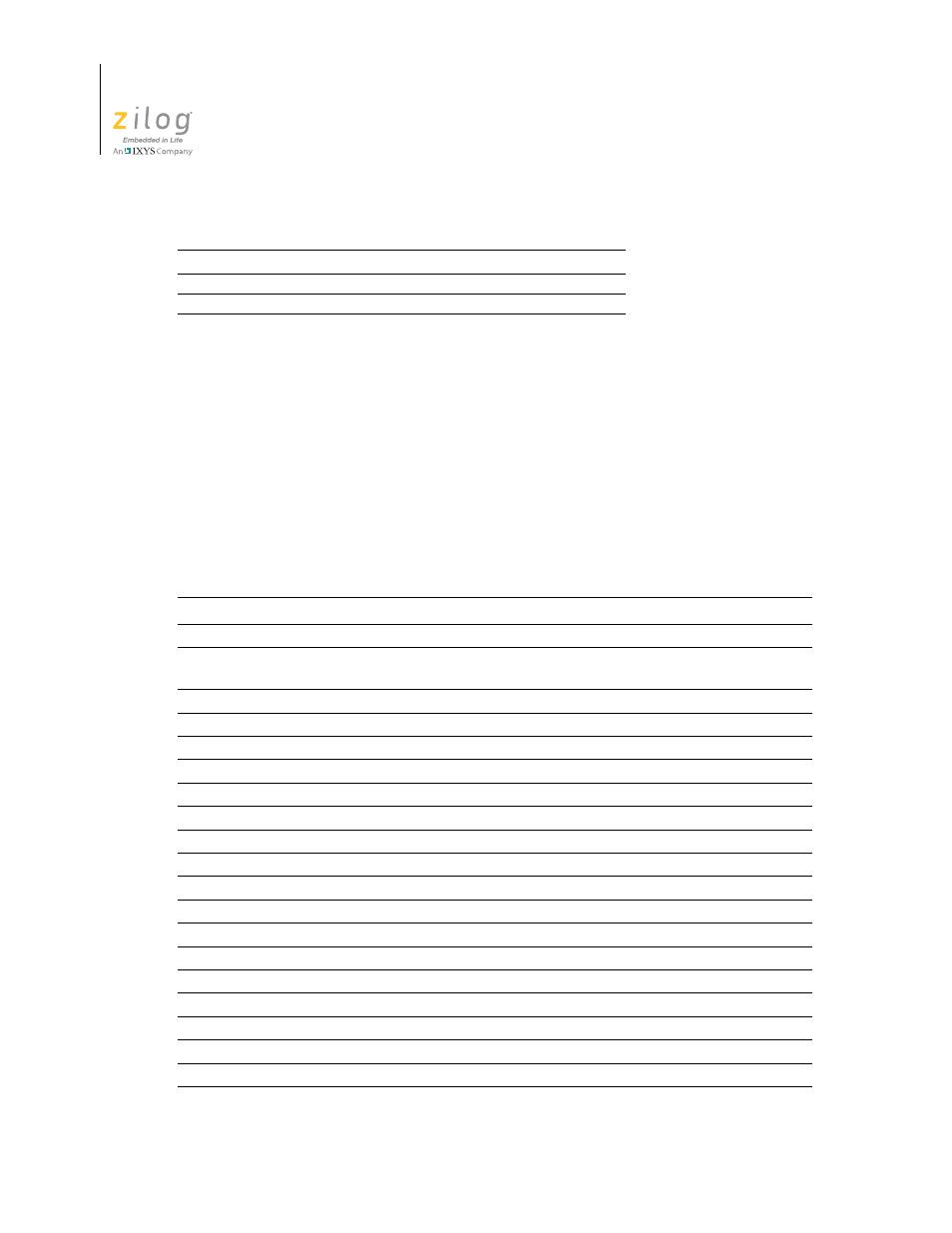

Flags

Syntax and Opcodes

7

6

5

4

3

2

1

0

C

Z

S

V

B

CIRQE IRQE

–

–

–

–

*

–

–

–

Legend

C

= No change.

Z

= No change.

S

= No change.

V

= No change.

B

= Set to one if the source is in memory and the source value is 0. Cleared to 0 if the source is in

memory and the source value is nonzero. No change if the source is a register or immediate value.

CIRQE

= No change.

IRQE

= No change.

Instruction, Operands

Word 0

Word 1

Word 2

LD Rd, #imm32

{452H, Rd}

imm[31:16]

imm[15:0]

LD Rd, #simm17

{45H, 000B,

simm[16], Rd}

simm[15:0]

LD Rd, #simm8

{3H, Rd, simm8}

LD Rd, Rs

{44H, Rs, Rd}

LD Rd, addr16

{034H, Rd}

addr16

LD Rd, addr32

{03CH, Rd}

addr[31:16]

addr[15:0]

LD Rd, (Rs)

{12H, Rs, Rd}

LD Rd, (Rs++)

{13H, Rs, Rd}

LD Rd, soff14(Rs)

{48H, Rs, Rd}

{0xB, soff14}

LD Rd, soff14(PC)

{002H, Rd}

{0xB, soff14}

LD Rd, soff6(FP)

{5H, 11B, soff6, Rd}

LD addr16, Rs

{037H, Rs}

addr16

LD addr32, Rs

{03FH, Rs}

addr[31:16]

addr[15:0]

LD (Rd), #imm32

{09DH, Rd}

imm[31:16]

imm[15:0]

LD (Rd), #simm16

{097H, Rd}

simm16

LD (Rd), Rs

{0BH, Rs, Rd}

LD soff14(Rd), Rs

{4AH, Rs, Rd}

{xxB, soff14}

LD soff6(FP), Rs

{5H, 10B, soff6, Rs}

LD (––Rd), #imm32

{09EH, Rd}

imm[31:16]

imm[15:0]

LD (––Rd), #simm16

{099H, Rd}

simm16