Loading an effective address, Figure 8, Register-indirect memory addressing example – Zilog Z16F2810 User Manual

Page 49

UM018809-0611

Operand Addressing

ZNEO

®

CPU Core

User Manual

33

Depending on the instruction, register-indirect addressing can be used for either the source

or destination operand, but a destination’s effective address must be a writable memory or

I/O location. The range allowed for the signed offset depends on the instruction used. For

the LD, CLR, CPZ, CPCZ, INC, and DEC instructions, the register-indirect offset range is

–4,096 to +4,095. For other instructions that accept an indirect offset, the range is –8,192

to +8,191.

For allowed JP and CALL offsets, see the

Several register-indirect instructions have alternate opcodes that do not accept an offset,

and therefore use fewer opcode words. When the offset is omitted in a register-indirect

operand, the ZNEO CPU uses the shorter instruction opcode if one is available.

Loading an Effective Address

The following assembly language statement is a an example of how you can initialize a

register with a base address:

LD R6, #FFFFB002H

Addresses in the range

FFFF_8000H

to

FFFF_FFFFH

are common because that is where

I/O memory and internal RAM are addressed, but using a 32-bit LD to initialize a register

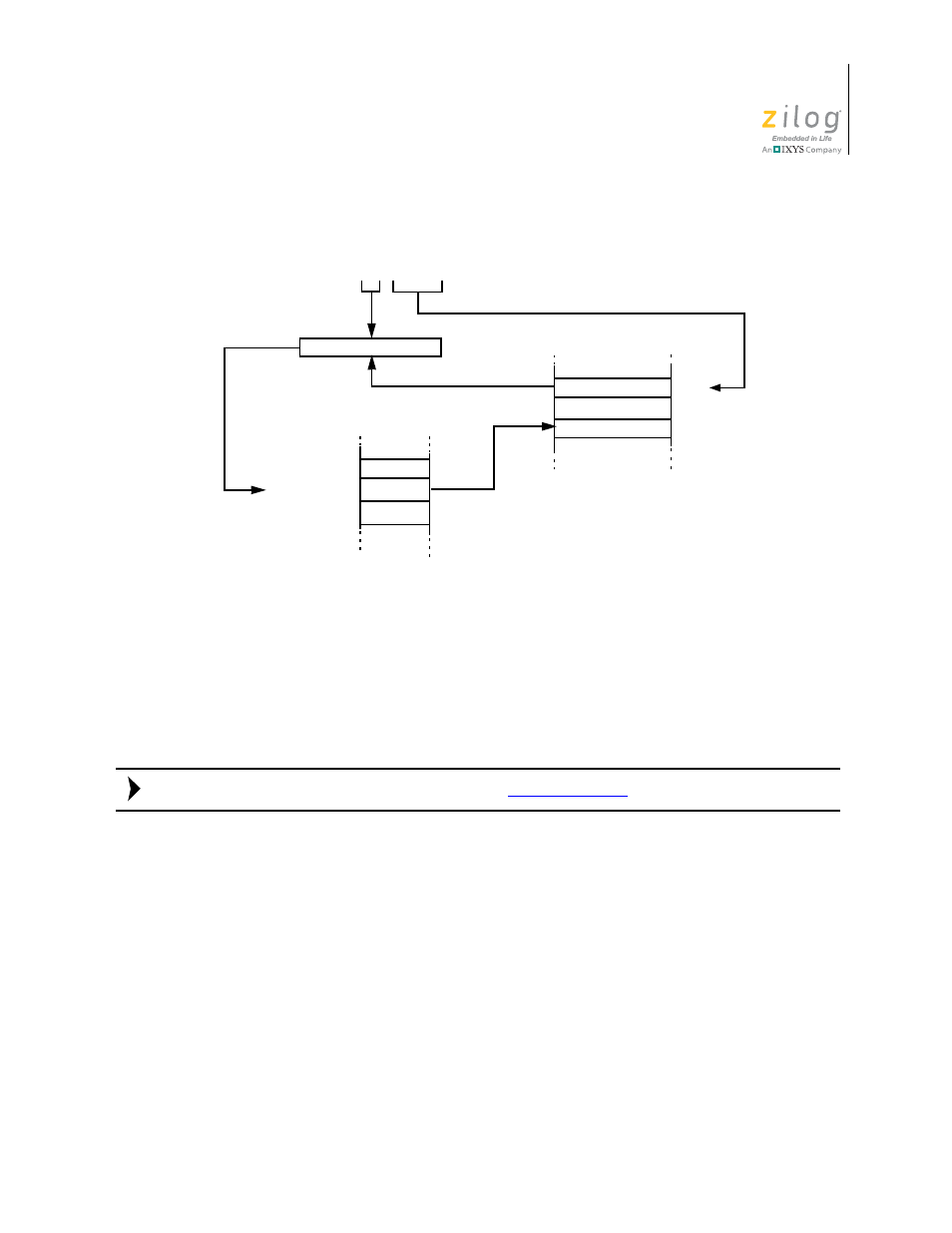

Figure 8. Register-Indirect Memory Addressing Example

LD.UB R10,4(R12)

42H

FFFF_7006H

R12

FFFF_7002H

4 + FFFF_7002H

32-Bit ALU Registers

Memory Space

Value Loaded:

42H

—

—

R11

—

R13

—

0000_0042H

R10

(Effective Address)

Note: