Sllx – Zilog Z16F2810 User Manual

Page 172

SLLX Instruction

UM018809-0611

156

ZNEO

®

CPU Core

User Manual

SLLX

Definition

Shift Left Logical, Extended

Syntax

SLLX dst, src

Operation

Description

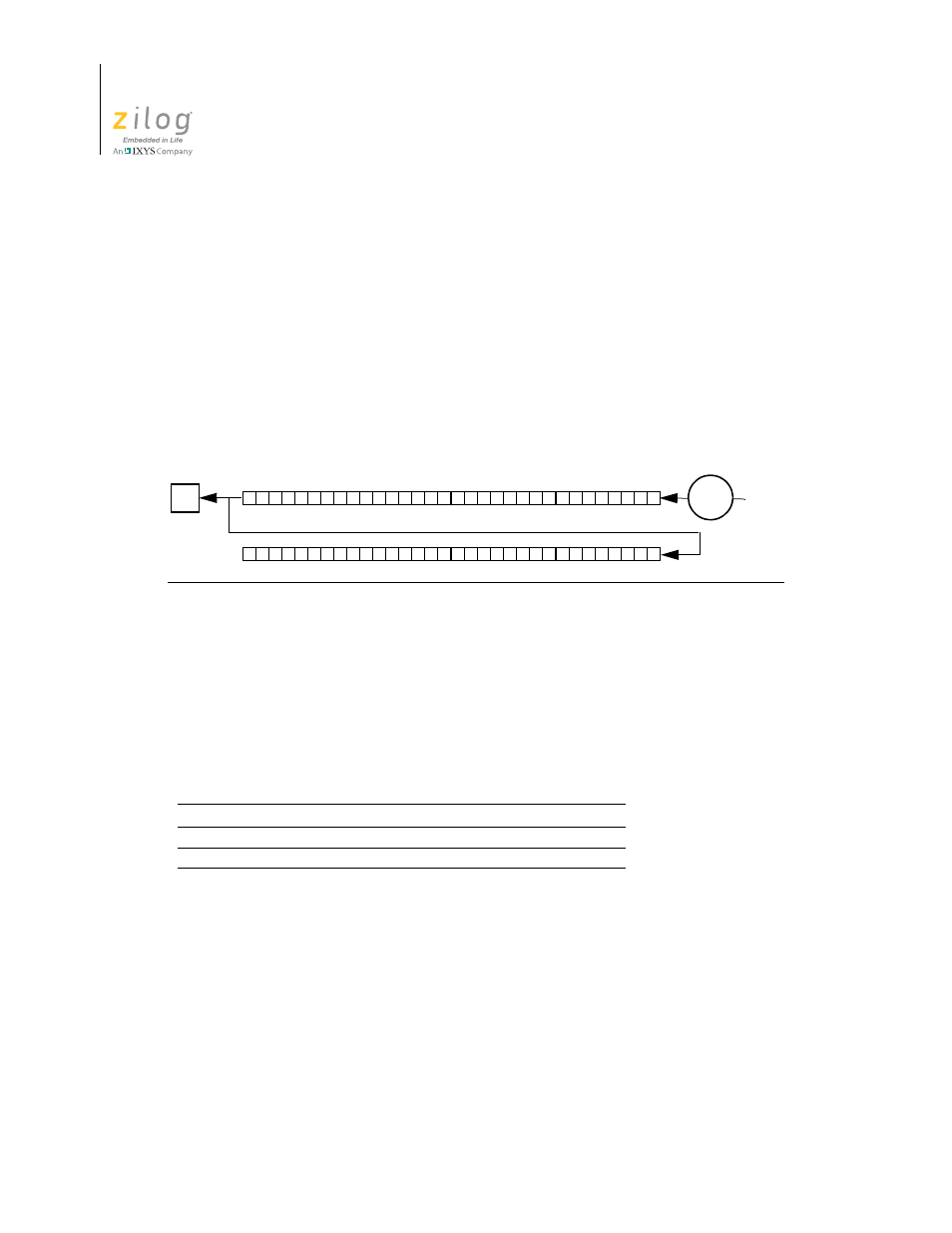

The destination operand contents shift left logical by the number of bit positions (0–31) specified

in bits [4:0] of the source operand. On each bit shift iteration, the value of the most significant bit

moves into the Carry (

C

) flag, and Bit 0 clears to 0.

The source register is cleared, and bits shifted out of the destination are shifted into the source

register. This instruction is generated by using the Extend prefix,

0007H

, with the SLL opcode.

Flags

7

6

5

4

3

2

1

0

C

Z

S

V

B

CIRQE IRQE

*

*

*

*

0

–

–

–

Legend

C

= Set to 1 if the last bit shifted out of the destination register is 1; otherwise set to 0.

Z

= Set to 1 if the 32-bit destination register contains zero; otherwise set to 0.

S

= Set to 1 if bit [31] of the destination register is 1; otherwise set to 0.

V

= Set to 1 if the Carry and Sign flags are different; otherwise set to 0.

B

= Cleared to 0.

CIRQE

= No change.

IRQE

= No change.

C

0

src

dst

31

0

src

31

0