Execution cycles, List of tables, Table 1 – Zilog Z16F2810 User Manual

Page 22: Instruction execution cycles

Architectural Overview

UM018809-0611

6

ZNEO

®

CPU Core

User Manual

Instructions always begin at an even address; therefore, instruction fetches are not subject

to uneven alignment delays.

An instruction fetch delay cycle can occur if the Fetch and Execution Units request access

to the same bus on the same cycle. In this case, the bus arbiter gives precedence to the

Execution Unit. This kind of delay can be avoided by storing instructions and data in dif-

ferent memory spaces; for example, instructions in ROM or Flash and data in RAM.

Execution Cycles

The minimum instruction execution time for most CPU instructions is one system clock

cycle. Additional cycles are required for shift, multiply, divide operations, and operations

which read or write memory locations. Table 1 lists minimum Execution Unit cycle times

for the various instructions. The symbol bus_time is described in the text following the

table, as other factors that affect execution of some instructions.

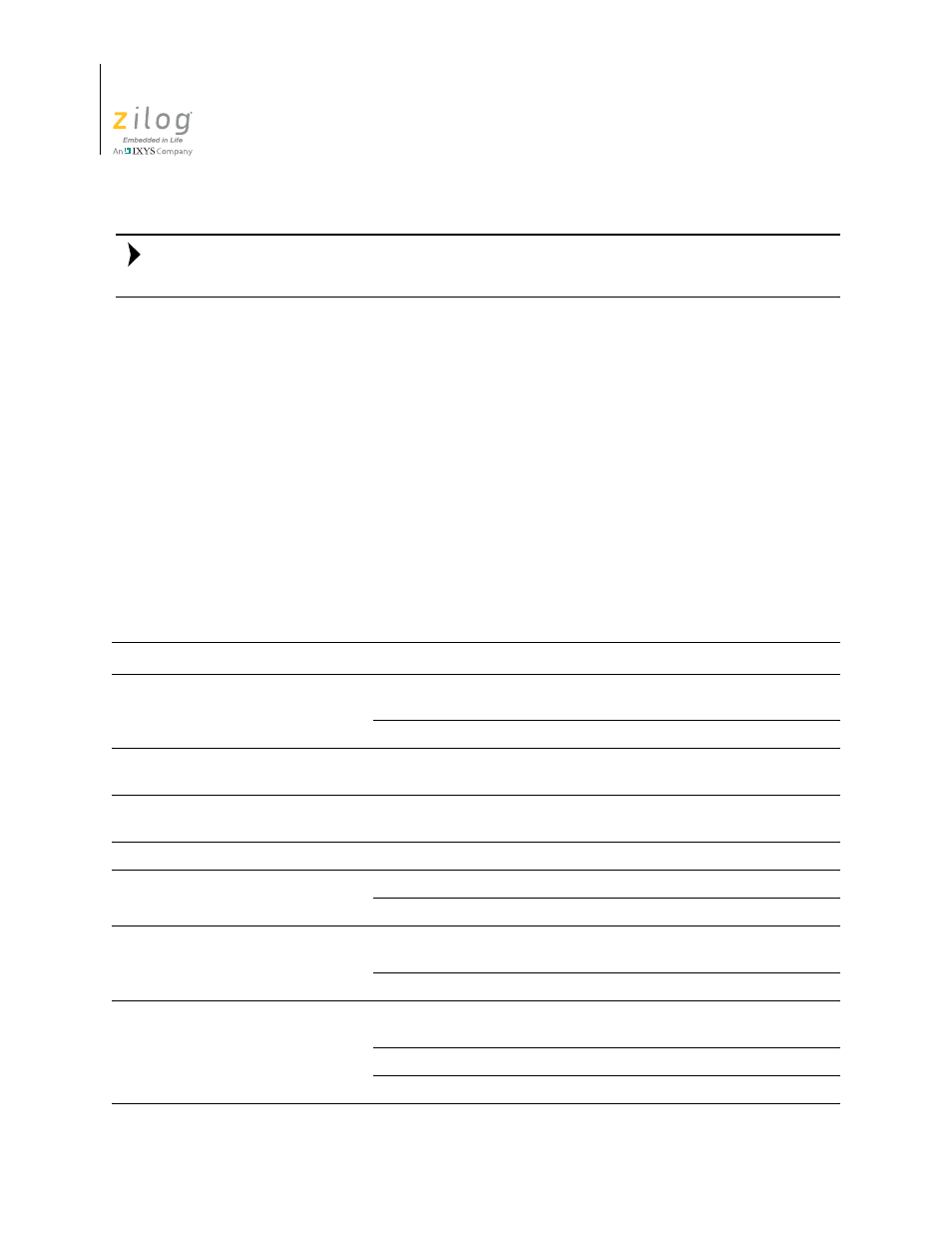

Table 1. Instruction Execution Cycles

Instruction

Operand Types

Minimum Execution Unit Cycles

LD, LEA

Immediate, Register-to-Reg-

ister

1

To or From Memory

1

bus_time

EXT, LDES, ATM, BRK, DI, DJNZ,

EI, HALT, IRET, NOP, RET, STOP

—

1

PUSH, POP,

PUSHF, POPF

—

1

bus_time

PUSHM, POPM

—

Variable

CLR

Register

1

Memory

1

bus_time

CP, CPZ, TM, TCM

Immediate, Register-to-Reg-

ister

1

To or From Memory

1 +

bus_time

ADC, ADD, AND, COM, CPC,

CPCZ, DEC, INC, NEG, OR, SBC,

SUB, XOR

Immediate, Register-to-Reg-

ister

1

Memory to Register

1 +

bus_time

Register to Memory

2

bus_time

Note: