Zilog Z16F2810 User Manual

Page 23

UM018809-0611

Architectural Overview

ZNEO

®

CPU Core

User Manual

7

Execution cycles can be affected by the following factors:

•

The symbol bus_time stands for the time to read or write a value to the addressed

memory bus, as given by the formula below:

(bus_wait_states + 1)

ceiling(data_bytes/bus_bytes)

In the above equation, the following points can be considered:

–

Bus wait states is configured for a bus to accommodate memory specifications.

The number of wait states is added to each memory read or write on that bus.

–

The ceiling function rounds up to the nearest integer. This accounts for a 1-byte

access on a 2-byte bus, which takes a full memory access cycle, not 1/2 cycle.

–

The data bytes value can be 1, 2 or 4, depending on the size of the addressed data

(for direct or register-indirect addressed memory).

–

The bus bytes value can be 1 or 2, for fetches from an 8-bit or 16-bit bus, respec-

tively.

An unaligned 16-bit or 32-bit read or write requires additional cycles. For more

details, see the

MUL, SMUL, UMUL

Operands

1_0000H

10

Operands 1_0000H

18

SDIV

Destination

1_0000H

17 if result is positive, 18 if negative

Destination 1_0000H

33 if result is positive, 34 if negative

UDIV

Destination

1_0000H

17

Destination 1_0000H

33

UDIV64

—

34

SRA, SRL, SLL, RL

—

(src/8) + (src % 8)

SRAX, SRLX, SLLX

—

src + 1

JP, JP cc, CALL, NOFLAGS, Extend

Prefix

—

0

ILL, TRAP

—

1 + 4

IROM_bus_time

+ 6

stack_bus_time

+ next_instruction_words

LINK

—

2 + 4

stack_bus_time

UNLINK

—

1 + 4

stack_bus_time

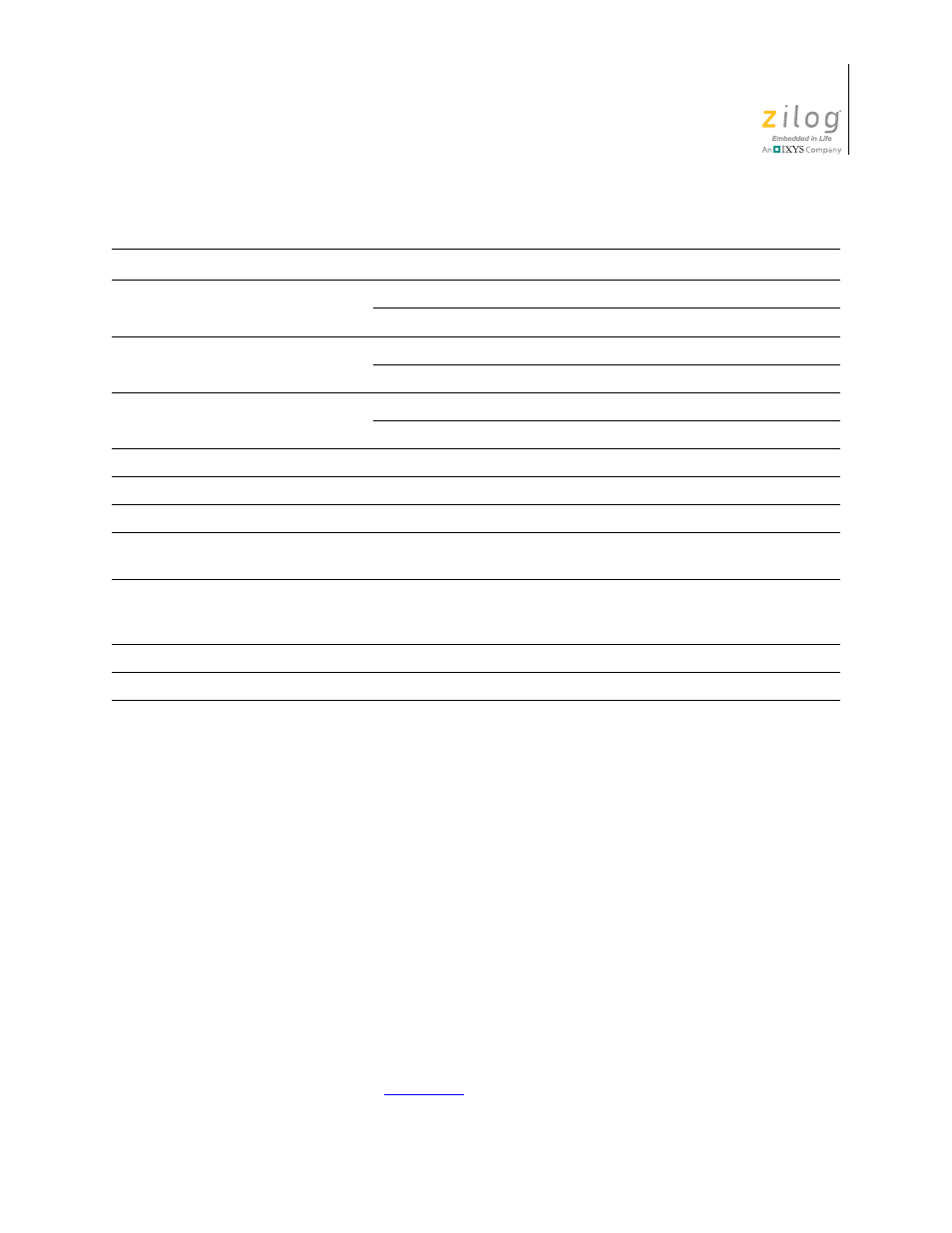

Table 1. Instruction Execution Cycles (Continued)

Instruction

Operand Types

Minimum Execution Unit Cycles