Altera RapidIO II MegaCore Function User Manual

Page 99

Chapter 4: Functional Description

4–57

Logical Layer Interfaces

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

Table 4–32

lists the Avalon-ST pass-through interface usage example this section

describes.

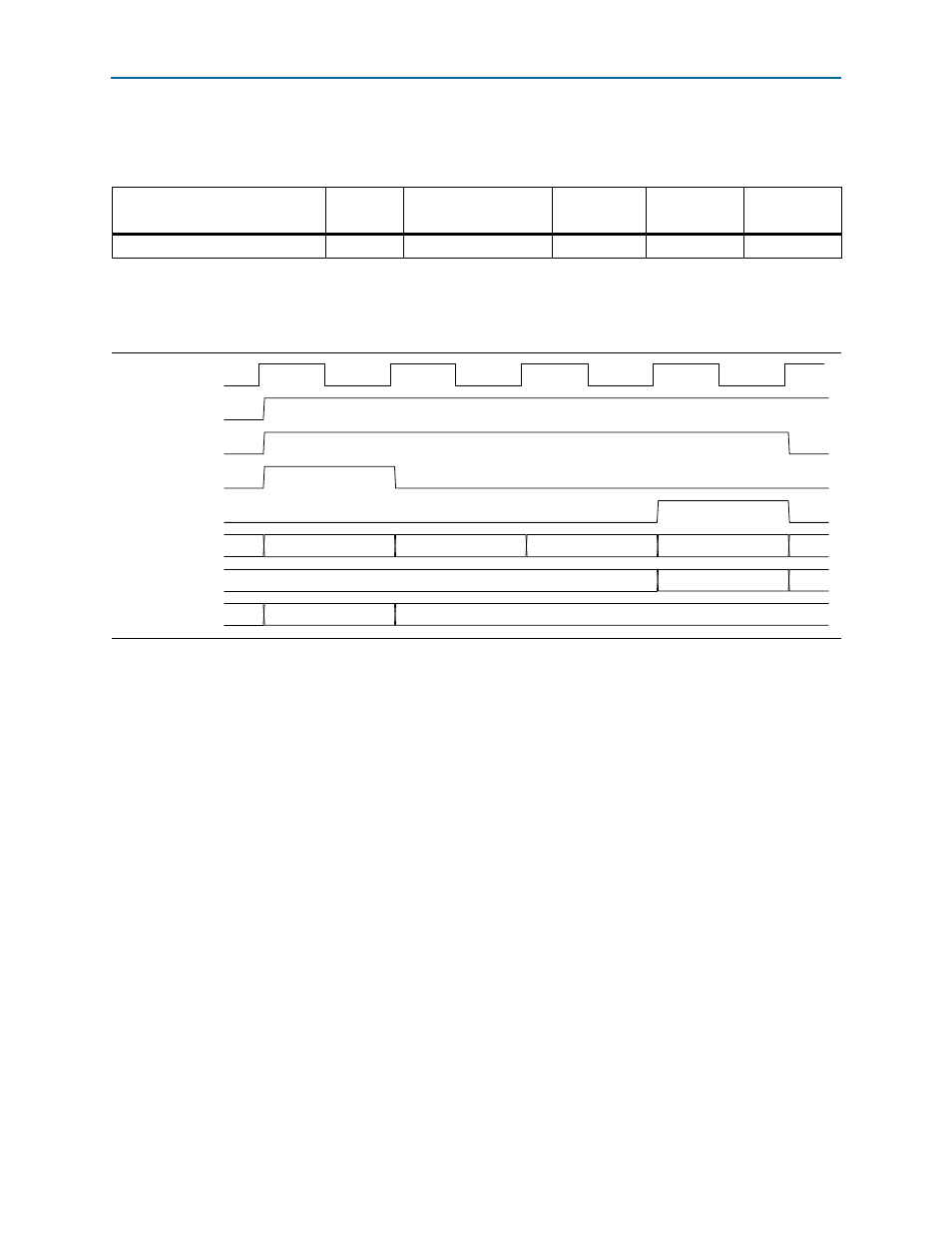

Figure 4–21

shows the behavior of the signals on the Avalon-ST pass-through

interface for this example transaction.

In the first clock cycle of the example, the IP core asserts gen_tx_ready to indicate it is

ready to sample data. In the same cycle, user logic asserts gen_tx_valid. Because both

gen_tx_ready

and gen_tx_valid are asserted, this clock cycle is an Avalon-ST ready

cycle. The user logic provides valid data on gen_tx_data for the IP core to sample, and

asserts gen_tx_startofpacket to indicate the current value of gen_tx_data is the

initial piece of the current packet (the start of packet). On gen_tx_packet_size, user

logic reports the full length of the packet is 0x32, which is decimal 50, because the

packet comprises 10 bytes of header and 40 bytes of payload data.

The user logic provides the 40-byte payload and 10-byte header on the same bus,

gen_tx_data[127:0]

. Transferring these 50 bytes of information requires four clock

cycles. During all of these cycles, the IP core holds gen_tx_ready high and user logic

holds gen_tx_valid high, indicating the cycles are all Avalon-ST ready cycles. In the

second and third cycles, user logic holds gen_tx_startofpacket and

gen_tx_endofpacket

low, because the information on gen_tx_data is neither start of

packet nor end of packet data. In the fourth clock cycle, user logic asserts

gen_tx_endofpacket

and sets gen_tx_empty to the value of 0xE to indicate that only

two of the bytes of data available on gen_tx_data in the current clock cycle are valid.

Table 4–32. Avalon-ST Pass-Through Interface Usage Example: Sending Write Request

User Operation

Operation

Type

RapidIO Transaction

Priority

Device ID

Width

Payload Size

(Bytes)

Send write request

Tx

NWRITE

0

8

40

Figure 4–21. Avalon-ST Pass-Through Interface NWRITE Transmit Example

clk

gen_tx_ready

gen_tx_valid

gen_tx_empty[3:0]

gen_tx_packet_size[8:0]

gen_tx_startofpacket

gen_tx_endofpacket

0005DDAA4C00FEDCBA94000102030405

0

032

060708090A0B0C0D0E0F101112131415

161718191A1B1C1D1E1F202122232425

26270000000000000000000000000000

E

gen_tx_data[127:0]