Altera RapidIO II MegaCore Function User Manual

Page 130

5–6

Chapter 5: Signals

Physical Layer Signals

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

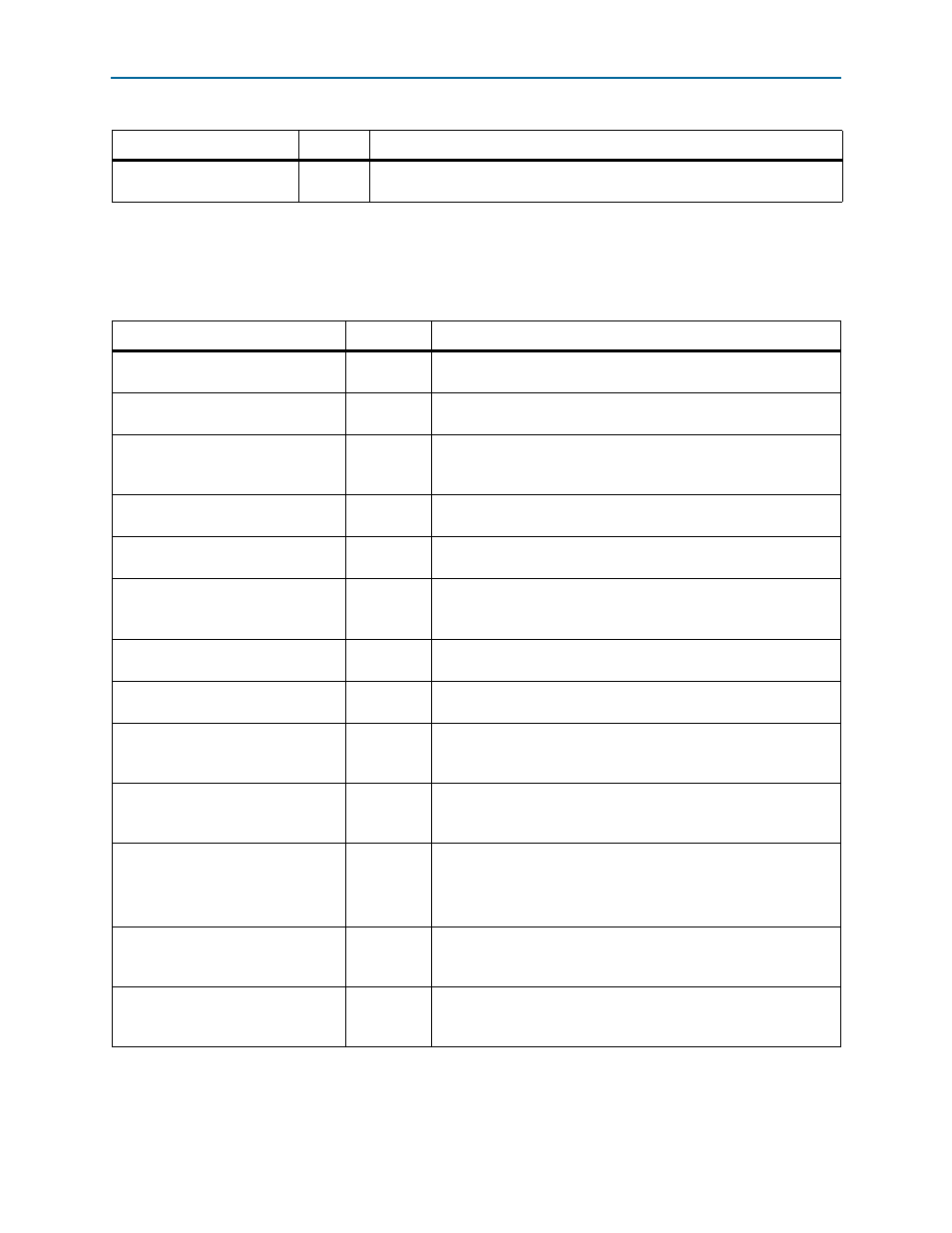

rx_signaldetect[n:0]

Output

Indicates that the lane detects a sender at the other end of the link: the signal is

above the programmed signal detection threshold value.

Note to

Table 5–7

:

(1) Refer to

“Instantiating Multiple RapidIO II IP Cores” on page 2–10

for information about how to successfully combine multiple high-speed

transceiver channels—whether in two RapidIO IP core instances or in a RapidIO IP core and in another component—in the same transceiver

block.

Table 5–7. Transceiver Signals (Part 2 of 2)

Signal Direction

Description

Table 5–8. Arria 10 Transceiver Dynamic Reconfiguration Avalon-MM Interface Signals (Part 1 of 3) (Part 1 of 3)

Signal

Direction

Description

reconfig_clk_ch0

Input

Arria 10 dynamic reconfiguration interface clock for the transceiver

channel configured for RapidIO lane 0.

reconfig_reset_ch0

Input

Arria 10 dynamic reconfiguration interface reset for the transceiver

channel configured for RapidIO lane 0.

reconfig_waitrequest_ch0

Output

Arria 10 dynamic reconfiguration slave wait request for the

transceiver channel configured for RapidIO lane 0. The RapidIO II IP

core uses this signal to stall the requestor on the interconnect.

reconfig_read_ch0

Input

Arria 10 dynamic reconfiguration slave read request for the

transceiver channel configured for RapidIO lane 0.

reconfig_write_ch0

Input

Arria 10 dynamic reconfiguration slave write request for the

transceiver channel configured for RapidIO lane 0.

reconfig_address_ch0[9:0]

Input

Arria 10 dynamic reconfiguration slave address bus for the

transceiver channel configured for RapidIO lane 0. The address is a

word address, not a byte address.

reconfig_writedata_ch0[31:0]

Input

Arria 10 dynamic reconfiguration slave write data bus for the

transceiver channel configured for RapidIO lane 0.

reconfig_readdata_ch0[31:0]

Output

Arria 10 dynamic reconfiguration slave read data bus for the

transceiver channel configured for RapidIO lane 0.

reconfig_clk_ch1

Input

Arria 10 dynamic reconfiguration interface clock for the transceiver

channel configured for RapidIO lane 1. This signal is available only in

2x and 4x variations.

reconfig_reset_ch1

Input

Arria 10 dynamic reconfiguration interface reset for the transceiver

channel configured for RapidIO lane 1. This signal is available only in

2x and 4x variations.

reconfig_waitrequest_ch1

Output

Arria 10 dynamic reconfiguration slave wait request for the

transceiver channel configured for RapidIO lane 1. The RapidIO II IP

core uses this signal to stall the requestor on the interconnect.

This signal is available only in 2x and 4x variations.

reconfig_read_ch1

Input

Arria 10 dynamic reconfiguration slave read request for the

transceiver channel configured for RapidIO lane 1. This signal is

available only in 2x and 4x variations.

reconfig_write_ch1

Input

Arria 10 dynamic reconfiguration slave write request for the

transceiver channel configured for RapidIO lane 1. This signal is

available only in 2x and 4x variations.