Avalon-mm – Altera RapidIO II MegaCore Function User Manual

Page 69

Chapter 4: Functional Description

4–27

Logical Layer Interfaces

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

Translation Window 2

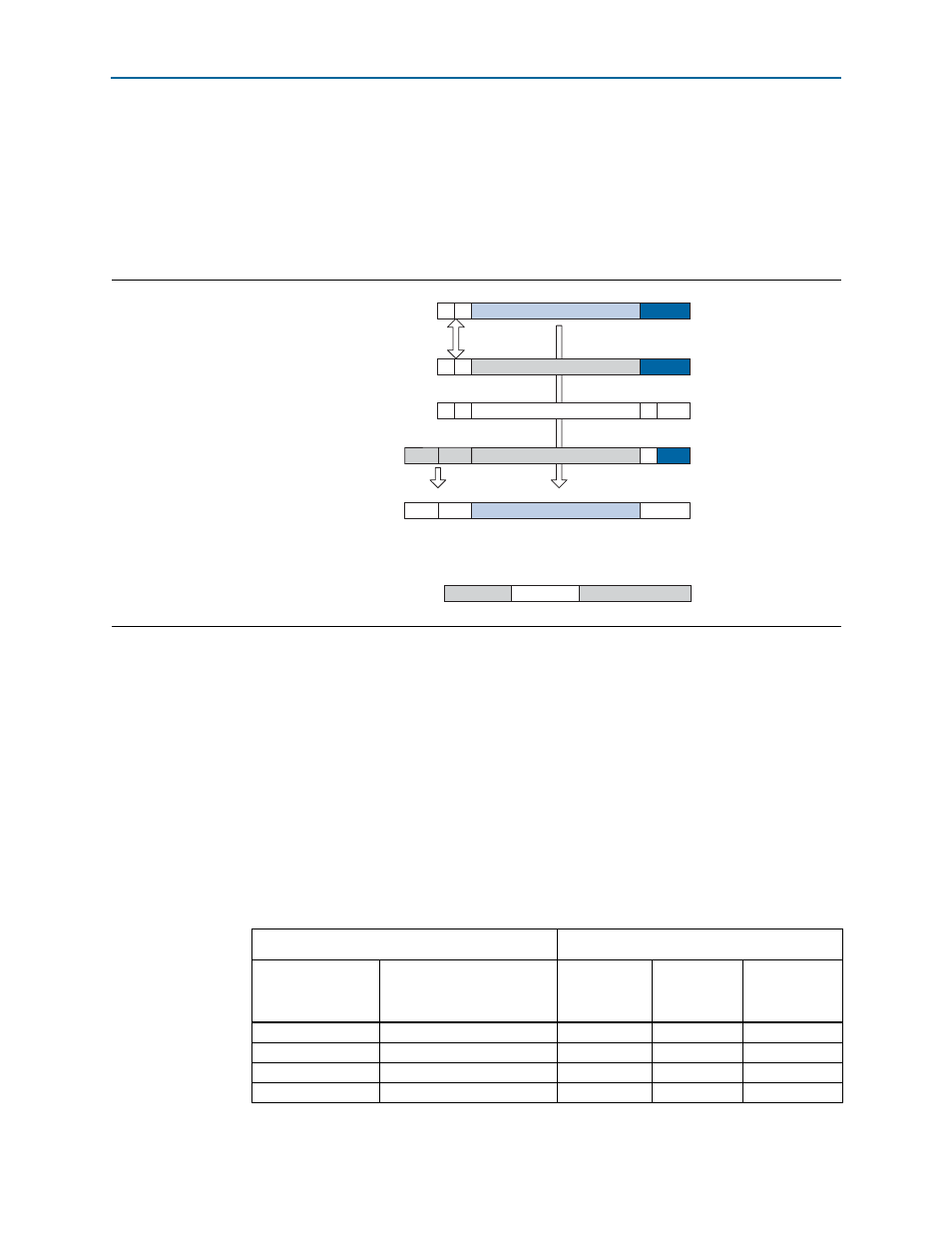

An Avalon-MM address in which the two most significant bits have a value of 2'b11

matches window 2. The RapidIO transaction corresponding to the Avalon-MM

operation has a destination ID value of 0xCC. This value corresponds to processing

endpoint 2.

shows address translation window 2.

Avalon-MM Burstcount and Byteenable Encoding in RapidIO Packets

The RapidIO II IP core converts Avalon-MM transactions to RapidIO packets. The IP

translates the Avalon-MM burst count, byteenable, and address bit 3 values to the

RapidIO packet read size, write size, and word pointer fields.

For information about the packet size encoding that the RapidIO II IP core

implements for read requests, refer to

and

. For information

about the packet size encoding that the RapidIO II IP core implements for write

requests, refer to

.

lists the allowed Avalon-MM ios_rd_wr_byteenable values if

ios_rd_wr_burstcount

has the value of 1, and the corresponding encoding in the

packet header fields of a RapidIO read or write request packet.

Figure 4–13. Translation Window 2

26’h3555999

26’h3555999

RapidIO Address [33:0]

Avalon Address [31:0]

1

0

0

0

Destination ID

Don’t Care

Don’t Care

0

2

3

3

000000000000000000..............00

Base (register 0x10420)

Mask (register 0x10424)

Offset (register 0x10428)

Control (register 0x1042C)

1

29

29

23

16

30

31

R

R

1

1

1

1

1

1

0

0

0

0

1

1

1

1

30

31

32

33

XAMO

0xCC

Table 4–10. I/O Logical Layer Slave Read or Write Request Size Encoding I (Part 1 of 2)

Avalon-MM Signal Values

RapidIO Header Field Values

burstcount

(5'dx,

128-bit units)

byteenable

(16'bxxxx_xxxx_xxxx_xxxx)

wdptr

(1'bx)

rdsize or

wrsize

(4'bxxxx)

address[0]

(rio_addr[3])

1

0000_0000_0000_0001

1

0011

0

1

0000_0000_0000_0010

1

0010

0

1

0000_0000_0000_0100

1

0001

0

1

0000_0000_0000_1000

1

0000

0