Altera RapidIO II MegaCore Function User Manual

Page 141

Chapter 6: Software Interface

6–3

Memory Map

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

lists all the registers in the

extended features address spaces and all of the implementation-defined address

spaces that are accessed through the Maintenance Avalon-MM slave interface.

lists the doorbell registers. The individual register

descriptions appear in the following sections.

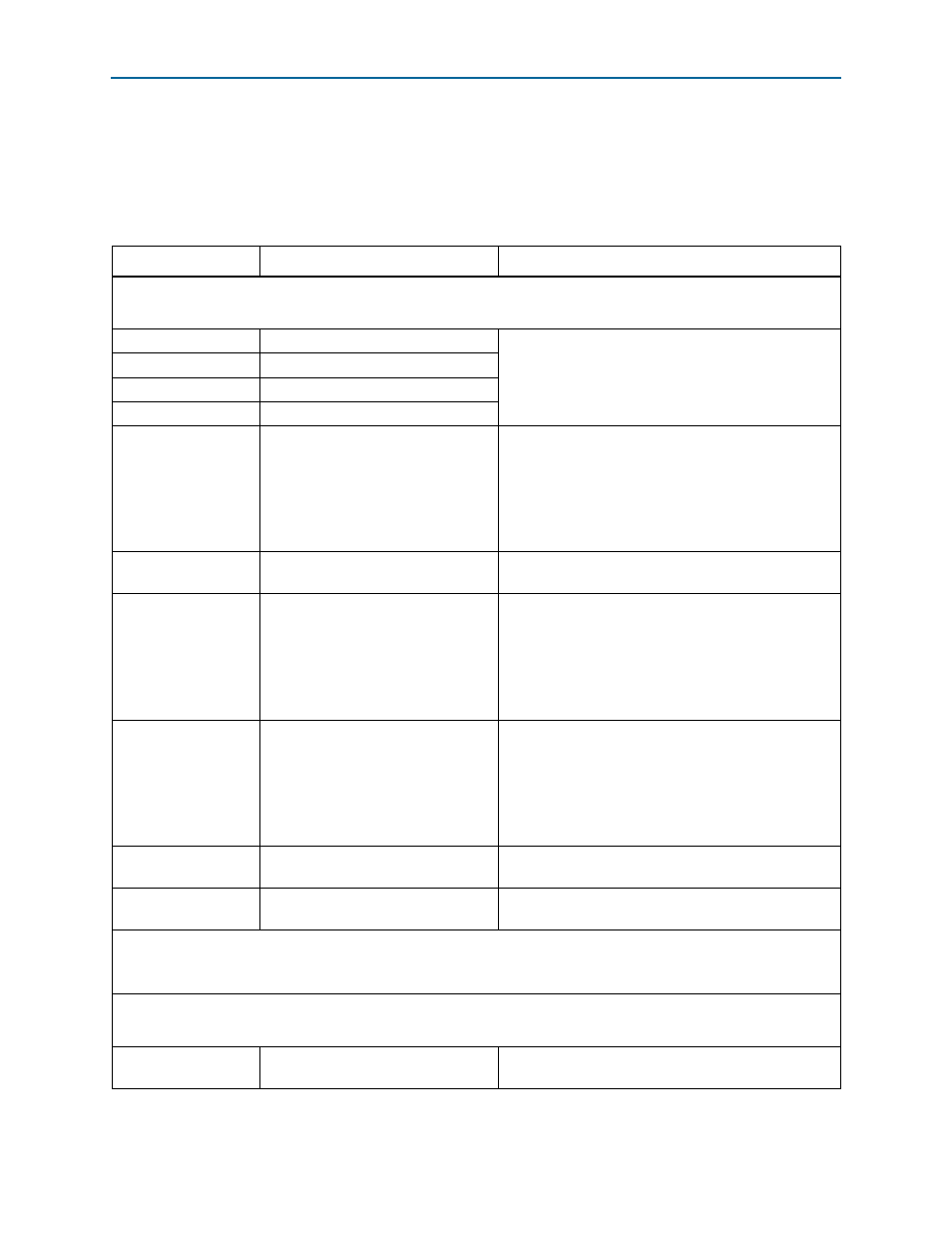

Table 6–3. CAR and CSR Memory Map (Part 1 of 2)

Address

Name

Register Specification Available in

Capability Registers (CARs)

These registers are described in

“Capability Registers (CARs)” on page 6–26

0x0

Device

Identity

RapidIO Interconnect Specification v2.2 Part 1:

Input/Output Logical Specification

0x4

Device

Information

0x8

Assembly

Identity

0xC

Assembly

Information

0x10

Processing

Element Features

■

RapidIO Interconnect Specification v2.2 Part 1:

Input/Output Logical Specification

■

RapidIO Interconnect Specification v2.2 Part 3:

Common Transport Specification

■

RapidIO Interconnect Specification v2.2 Part 6:

LP-Serial Physical Layer Specification

0x14

Switch

Port Information

RapidIO Interconnect Specification v2.2 Part 1:

Input/Output Logical Specification

0x18

Source

Operations

■

RapidIO Interconnect Specification v2.2 Part 1:

Input/Output Logical Specification

■

RapidIO Interconnect Specification v2.2 Part 2:

Message Passing Logical Specification

■

RapidIO Interconnect Specification v2.2 Part 10: Data

Streaming Logical Specification

0x1C

Destination

Operations

■

RapidIO Interconnect Specification v2.2 Part 1:

Input/Output Logical Specification

■

RapidIO Interconnect Specification v2.2 Part 2:

Message Passing Logical Specification

■

RapidIO Interconnect Specification v2.2 Part 10: Data

Streaming Logical Specification

0x34

Switch Route Table Destination

ID Limit

RapidIO Interconnect Specification Part 3: Common

Transport Specification

0x3C

Data Streaming Information

RapidIO Interconnect Specification v2.2 Part 10: Data

Streaming Logical Specification

(1) The CARs are not used by any of the RapidIO II IP core internal modules. They do not affect the functionality of the RapidIO II IP core. These

registers are all Read-Only. Their values are set using the RapidIO II parameter editor when generating the IP core, or with configuration input

signals, which should not change value during normal operation. These registers inform either a local processor or a processor on a remote

end about the IP core's capabilities.

Command and Status Registers (CSRs)

These registers are described in

“Command and Status Registers (CSRs)” on page 6–32

0x48

Data Streaming Logical Layer

Control

RapidIO Interconnect Specification v2.2 Part 10: Data

Streaming Logical Specification