Altera RapidIO II MegaCore Function User Manual

Page 143

Chapter 6: Software Interface

6–5

Memory Map

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

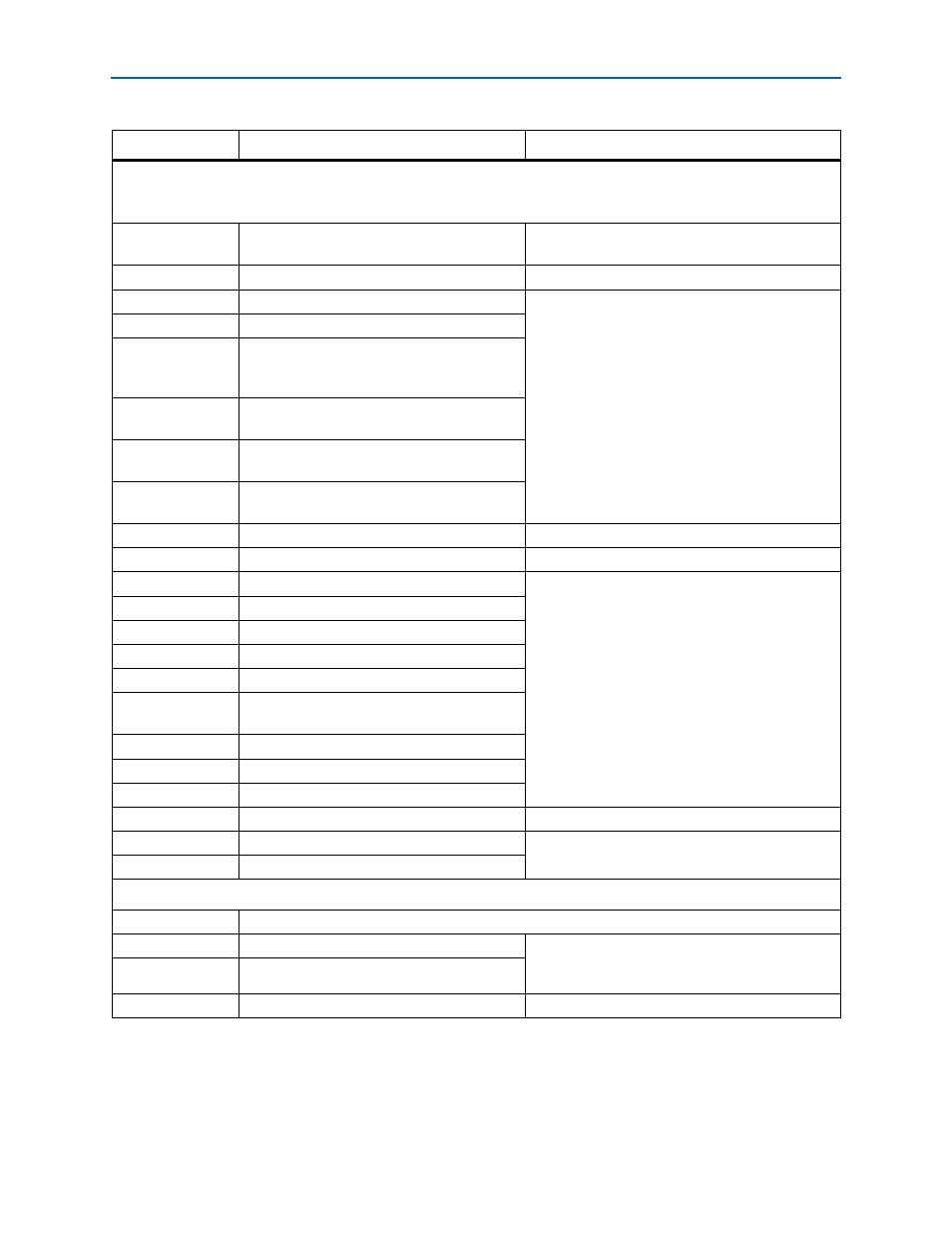

Extended Features Space: Error Management Extensions

These registers are defined in the RapidIO Interconnect Specification Part 8: Error Management Extensions Specification

and described in

“Error Management Registers” on page 6–42

0x300

Error Management Extensions Block

Header

0x304

Reserved

0x308

Logical/Transport

Layer Error Detect

Logical/Transport layer

0x30C

Logical/Transport

Layer Error Enable

0x310

Logical/Transport

Layer High Address

Capture

— Reserved — RapidIO II IP core

has only 34-bit RapidIO addressing

0x314

Logical/Transport

Layer Address

Capture

0x318

Logical/Transport

Layer Device ID

Capture

0x31C

Logical/Transport

Layer Control

Capture

0x320–0x324

Reserved

0x328

Port-Write Target Device ID

Maintenance module

0x32C

Packet Time-to-Live

Physical layer

0x330–0x33C

Reserved

0x340

Port 0 Error Detect

0x344

Port 0 Error Rate Enable

0x348

Port 0 Attributes Capture

0x34C

Port 0 Packet/Control Symbol Capture

0

0x350

Port 0 Packet Capture 1

0x354

Port 0 Packet Capture 2

0x358

Port 0 Packet Capture 3

0x35C–0x364

Reserved

0x368

Port 0 Error Rate

Physical layer

0x36C

Port 0 Error Rate Threshold

Implementation-Defined Space

0x10000-0x1007C

Reserved

0x10080

Maintenance

Interrupt

Maintenance module. These registers are described

in

“Maintenance Interrupt Control Registers” on

0x10084

Maintenance

Interrupt Enable

0x10088–0x100FC

Reserved

Table 6–4. Extended Features and Implementation-Defined Registers Memory Map (Part 2 of 3)

Address

Name

Used by Module