Ip core verification, Simulation testing, Ip core verification –5 – Altera RapidIO II MegaCore Function User Manual

Page 13: Simulation testing –5

Chapter 1: About The RapidIO II MegaCore Function

1–5

IP Core Verification

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

shows the level of support offered by the RapidIO II IP core for each Altera

device family.

IP Core Verification

Before releasing a publicly available version of the RapidIO II IP core, Altera runs a

comprehensive verification suite in the current version of the Quartus

®

II software.

These tests use standalone methods and the Qsys system integration tool to create the

instance files. These files are tested in simulation and hardware to confirm

functionality. Altera tests and verifies the RapidIO II MegaCore function in hardware

for different platforms and environments.

Altera also performs interoperability testing to verify the performance of the IP core

and to ensure compatibility with ASSP devices.

Simulation Testing

Altera verifies the RapidIO II IP core using the following industry-standard

simulators:

■

ModelSim

®

simulator

■

VCS

The test suite contains testbenches that use the Cadence Serial RapidIO Verification IP

(VIP), the Cadence Compliance Management System (CMS) implementation of the

RapidIO Trade Association interoperability checklist, and the RapidIO bus functional

model (BFM) from the RapidIO Trade Association to verify the functionality of the IP

core.

The test suite confirms various functions, including the following functionality:

■

Link initialization

■

Packet format

■

Packet priority

■

Error handling

■

Throughput

■

Flow control

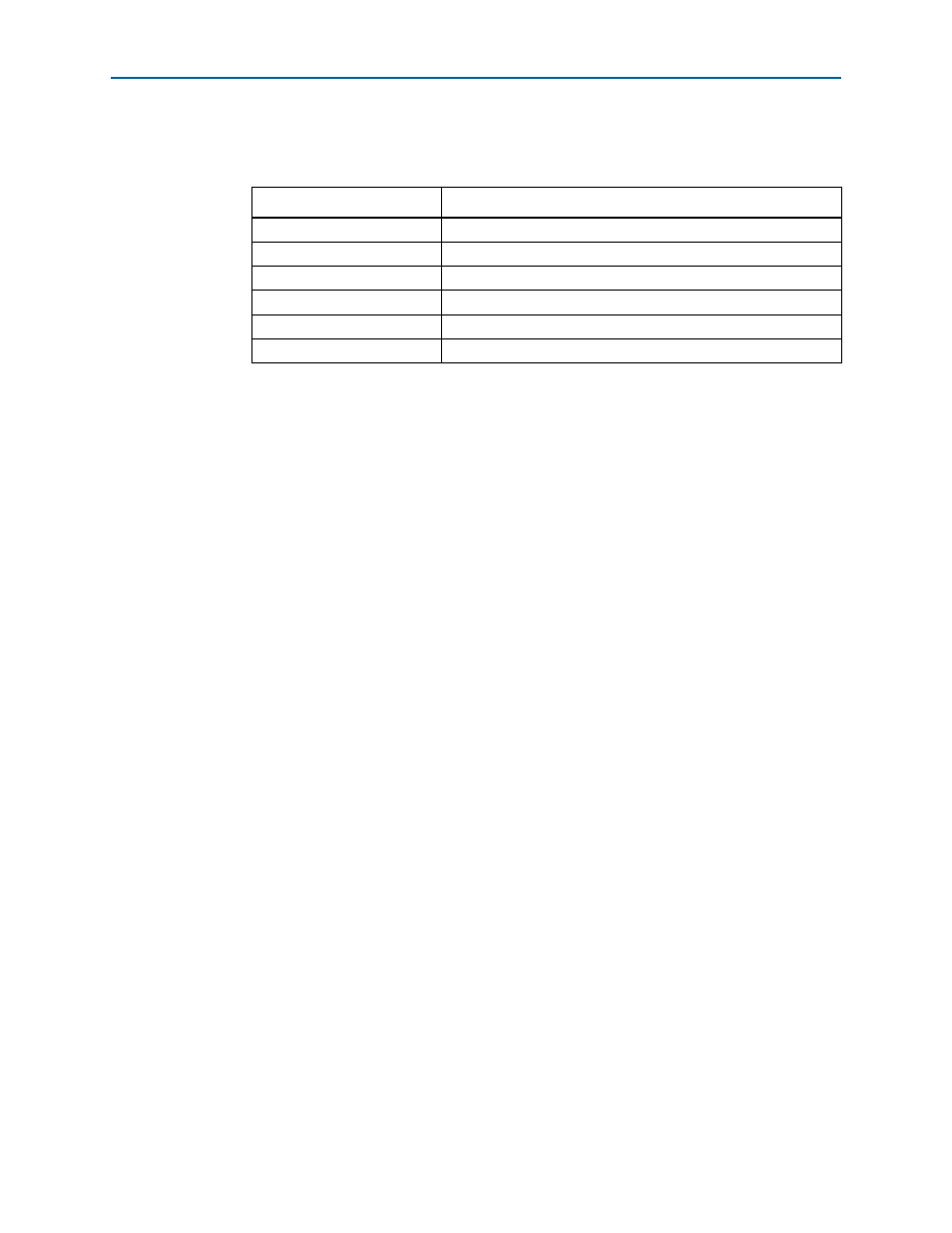

Table 1–2. Device Family Support

Device Family

Support

Arria 10

Refer to

page of the Altera website.

Arria V (GX and GT)

Final

Arria V GZ

Final

Cyclone V

Final

Stratix V

Final

Other device families

No support