Altera RapidIO II MegaCore Function User Manual

Page 158

6–20

Chapter 6: Software Interface

Physical Layer Registers

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

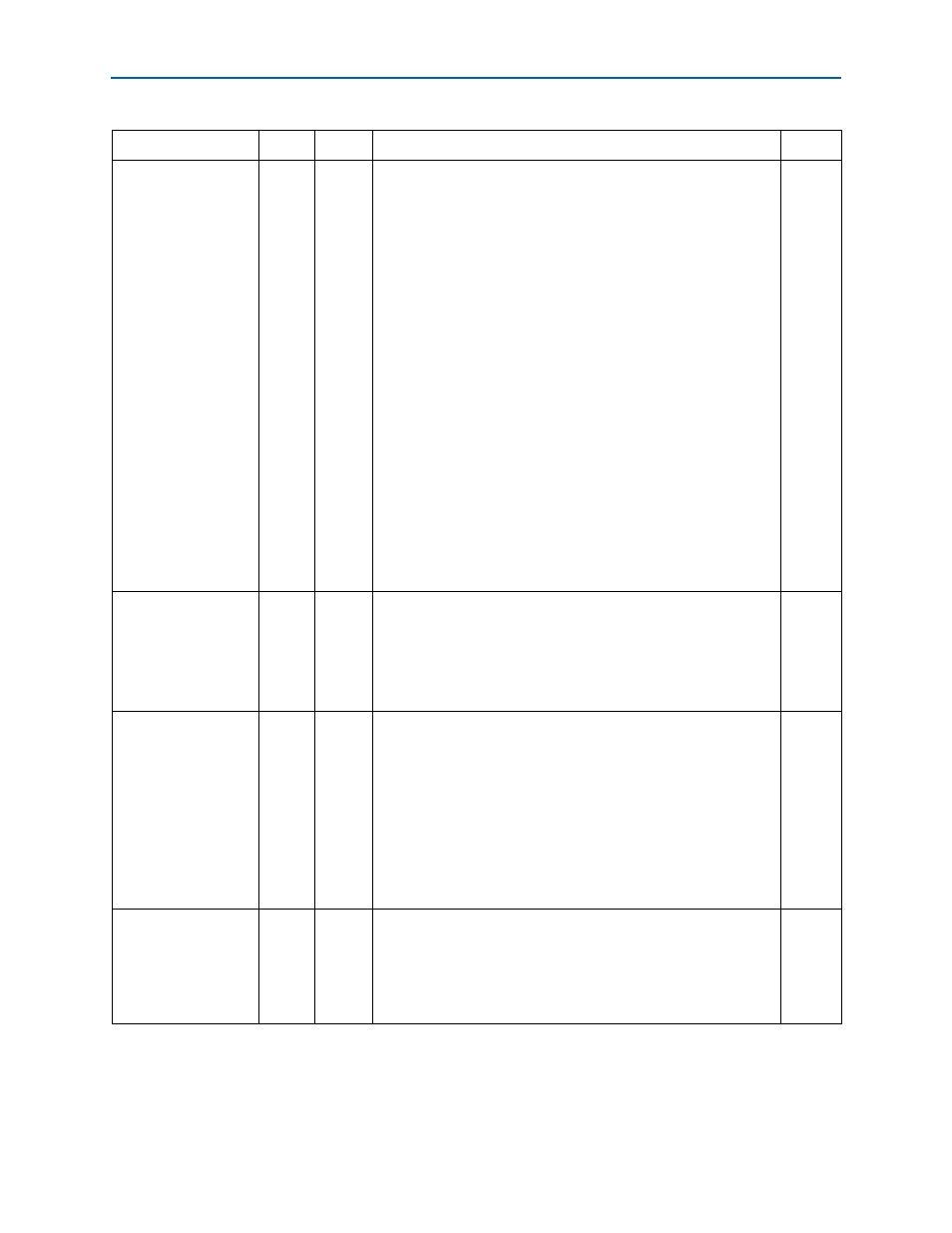

STOP_ON_PRT_FAIL_

ENCOUNTER_ENABLE

[3]

RW

Together with the DROP_PKT_ENABLE field, specifies the behavior of

the port when the failed error threshold in the Port 0 Error Rate

Threshold

register (offset 0x36C) has been reached or exceeded.

The RapidIO II IP core supports the following valid values for

{STOP_ON_PRT_FAIL_ENCOUNTER_ENABLE, DROP_PKT_ENABLE}:

2'b00—The port continues to attempt to transmit packets to the

RapidIO link partner.

2'b01—The port discards packets that receive a

packet-not-accepted

response. When the port discards a

packet, it sets the OUT_PKT_DROPD bit in the Port 0 Error and

Status

CSR (offset 0x158). The port resumes normal operation

when the value in the Error Rate Counter field of the Port 0

Error Rate

CSR (offset 0x368) falls below the failed error

threshold. This value is valid only for switch devices.

2’b10—The port stops trying to send packets to the link partner,

until software resets the OUT_FAIL_ENC field of the Port 0

Error and Status

CSR (offset 0x158). The IP core does apply

backpressure to ensure the queues do not overflow.

2’b11—The port discards all output packets, until software resets

the OUT_FAIL_ENC field of the Port 0 Error and Status CSR

(offset 0x158). When the port discards a packet, it sets the

OUT_PKT_DROPD

bit in the Port 0 Error and Status CSR.

1'b0

DROP_PKT_ENABLE

[2]

RW

Together with the STOP_ON_PRT_FAIL_ENCOUNTER_ENABLE field,

specifies the behavior of the port when the failed error threshold in

the Port 0 Error Rate Threshold register (offset 0x36C) has

been reached or exceeded.

Refer to the description of the

STOP_ON_PRT_FAIL_ENCOUNTER_ENABLE

field.

1'b0

PORT_LOCKOUT

[1]

RW

This bit indicates whether the port is stopped or the IN_PENA (bit

[21]) and OUT_PENA (bit [22]) register fields control the port:

1'b0—The Input Port Enable (IN_PENA) and Output Port Enable

(OUT_PENA) fields in this register control which packets the port

may receive and transmit on the RapidIO link.

1'b1—Port is stopped and is not enabled to issue or receive any

packets. The input port can still follow the training procedure and

can still send and respond to link-requests. All received packets

return packet-not-accepted control symbols to force an error

condition to be signaled by the sending device.

1'b0

PORT_TYPE

[0]

RO

Indicates the port type, parallel or serial.

1'b0—Parallel port.

1'b1—Serial port.

The RapidIO II IP core supports only serial ports, so this bit always

has the value of 1’b1.

1'b1

Note to

:

(1) Reflects the choice made in the RapidIO II parameter editor.

Table 6–15. Port 0 Control CSR—Offset: 0x15C (Part 4 of 4)

Field

Bits

Access

Function

Default