Altera RapidIO II MegaCore Function User Manual

Page 102

4–60

Chapter 4: Functional Description

Logical Layer Interfaces

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

User Sending Read Request and Receiving Read Response

lists the Avalon-ST pass-through interface usage example this section

describes. Refer to

“Transaction ID Ranges” on page 4–48

for a description of the RapidIO II IP core variations in which this example

transaction is processed through the Avalon-ST pass-through interface rather than

being processed through one of the I/O Logical layer modules.

sourceID[15:0]

[79:64]

16’h00AA

For variations with an 8-bit device ID, bits [79:72] (bits

[15:8] of the sourceID) are set to 8’h00.

ttype[3:0]

[63:60]

4’b0100

The value of 4 indicates an NWRITE transaction.

size[3:0]

[59:56]

4’b1100

The size and wdptr values encode the maximum size

of the payload field. In this example, they decode to a

value of 64 bytes. For details, refer to Table 4-4 in Part

1: Input/Output Logical Specification of the RapidIO

Interconnect Specification, Revision 2.2.

transactionID[7:0]

[55:48]

0

Not used for NWRITE transactions.

address[28:0]

[47:19]

{28’hFEDCBA9,

1’b0}

wdptr

[18]

1

Refer to the comment for size.

xamsbs[1:0]

[17:16]

2’b00

Reserved[15:0]

[15:0]

16’h0000

Table 4–35. NWRITE Request Receive Example: RapidIO Header Fields in gen_rx_hd_data Bus (Part 2 of 2)

Field

gen_rx_hd_data

Bits

Value

Comment

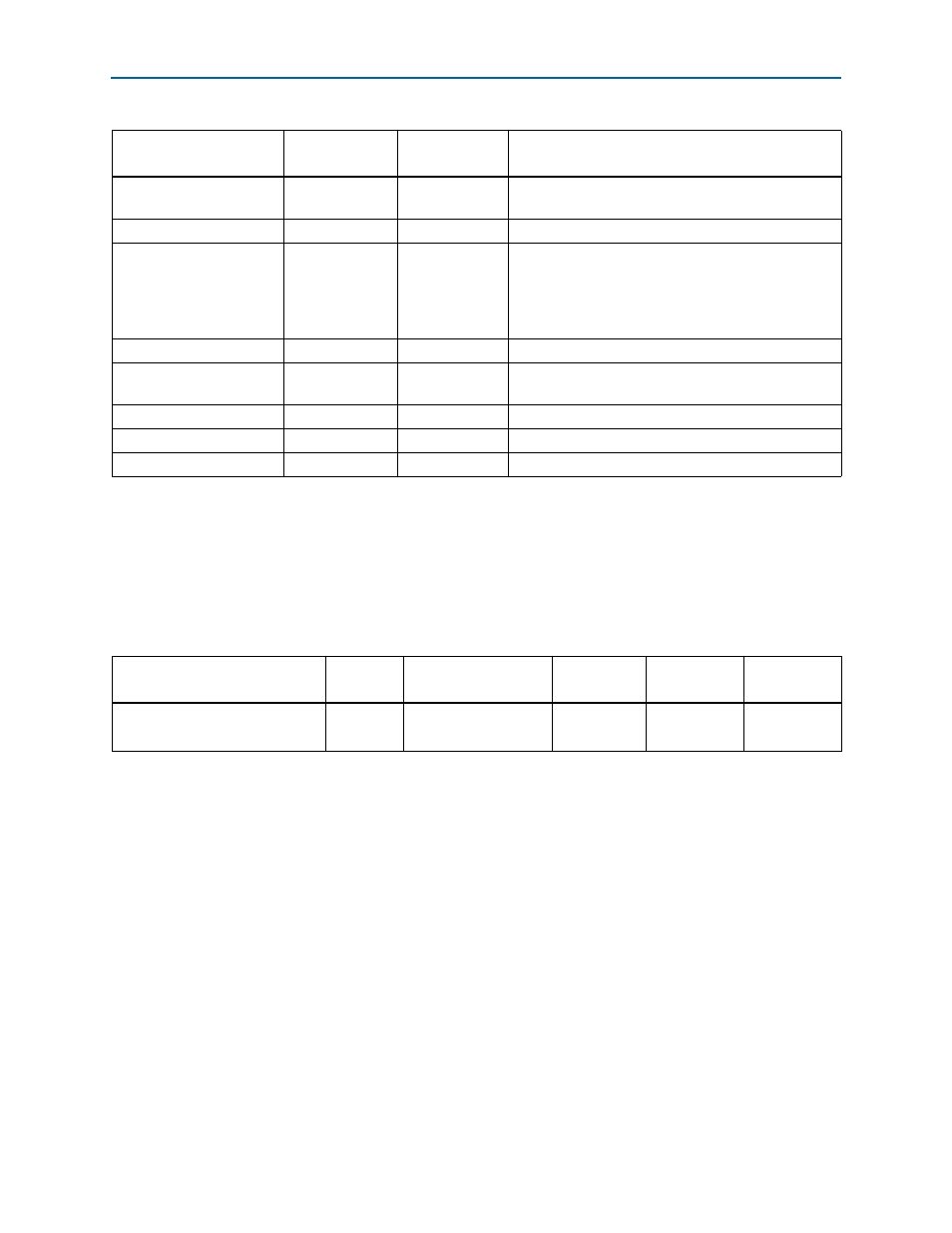

Table 4–36. Avalon-ST Pass-Through Interface Usage Example: Sending Read Request and Receiving Response

User Operation

Operation

Type

RapidIO Transaction

Priority

Device ID

Width

Payload Size

(Bytes)

Send read request

Tx

NREAD

1

16

32

Receive read response

Rx

Response with payload

2

16

32