Functional description, Interfaces, Avalon-mm interface byte ordering – Altera RapidIO II MegaCore Function User Manual

Page 43: Chapter 4. functional description, Interfaces –1, Avalon-mm interface byte ordering –1

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

4. Functional Description

Interfaces

The Altera RapidIO II IP core supports the following data interfaces:

■

Avalon Memory Mapped (Avalon-MM) Master and Slave Interfaces

■

Avalon Streaming (Avalon-ST) Interface

■

Avalon Memory Mapped (Avalon-MM) Master and Slave Interfaces

The Avalon-MM master and slave interfaces execute transfers between the RapidIO II

IP core and the system interconnect. The system interconnect allows you to use the

Qsys system integration tool to connect any master peripheral to any slave peripheral,

without detailed knowledge of either the master or slave interface. The RapidIO II IP

core implements both Avalon-MM master and Avalon-MM slave interfaces.

f

For more information about the Avalon-MM interface, refer

Avalon-MM Interface Byte Ordering

The RapidIO protocol uses big endian byte ordering, whereas Avalon-MM interfaces

use little endian byte ordering.

shows the byte ordering for the 64-bit

Avalon-MM interface and the RapidIO interface.

No byte- or bit-order swaps occur between the 64-bit Avalon-MM protocol and

RapidIO protocol, only byte- and bit-number changes. For example, RapidIO Byte0 is

Avalon-MM Byte7, and for all values of i from 0 to 63, bit i of the RapidIO 64-bit

double word[0:63] of payload is bit (63-i) of the Avalon-MM 64-bit double word[63:0].

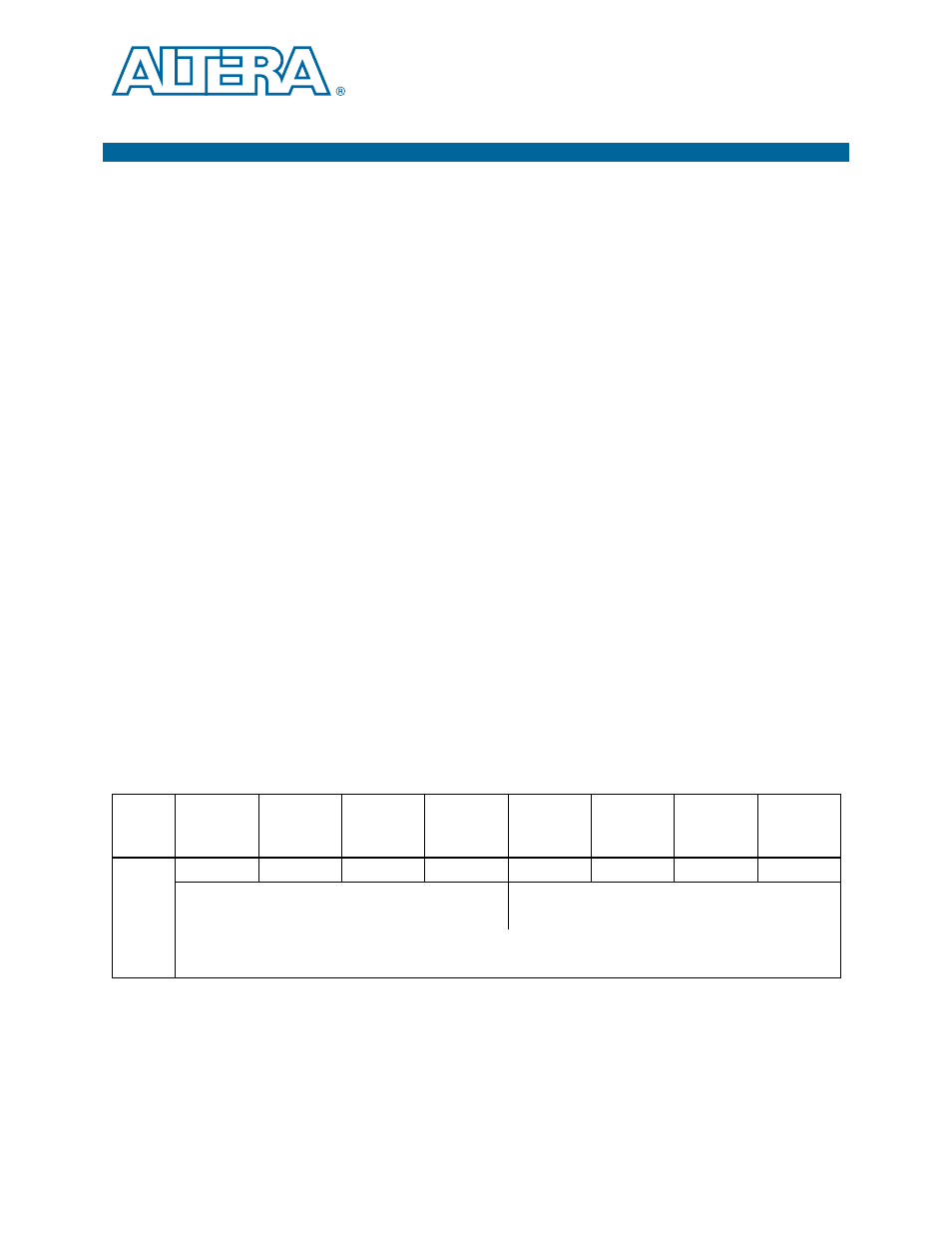

Table 4–1. Byte Ordering (Part 1 of 2)

Byte

Lane

(Binary)

1000_0000

0100_0000

0010_0000

0001_0000

0000_1000

0000_0100

0000_0010

0000_0001

RapidIO

Protocol

(Big

Endian)

Byte0[0:7]

Byte1[0:7]

Byte2[0:7]

Byte3[0:7]

Byte4[0:7]

Byte5[0:7]

Byte6[0:7]

Byte7[0:7]

32-Bit Word[0:31]

32-Bit Word[0:31]

wdptr=0

wdptr=1

Double Word[0:63]

RapidIO Byte Address N = {29'hn, 3'b000}