Altera RapidIO II MegaCore Function User Manual

Page 136

5–12

Chapter 5: Signals

Error Management Extension Signals

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

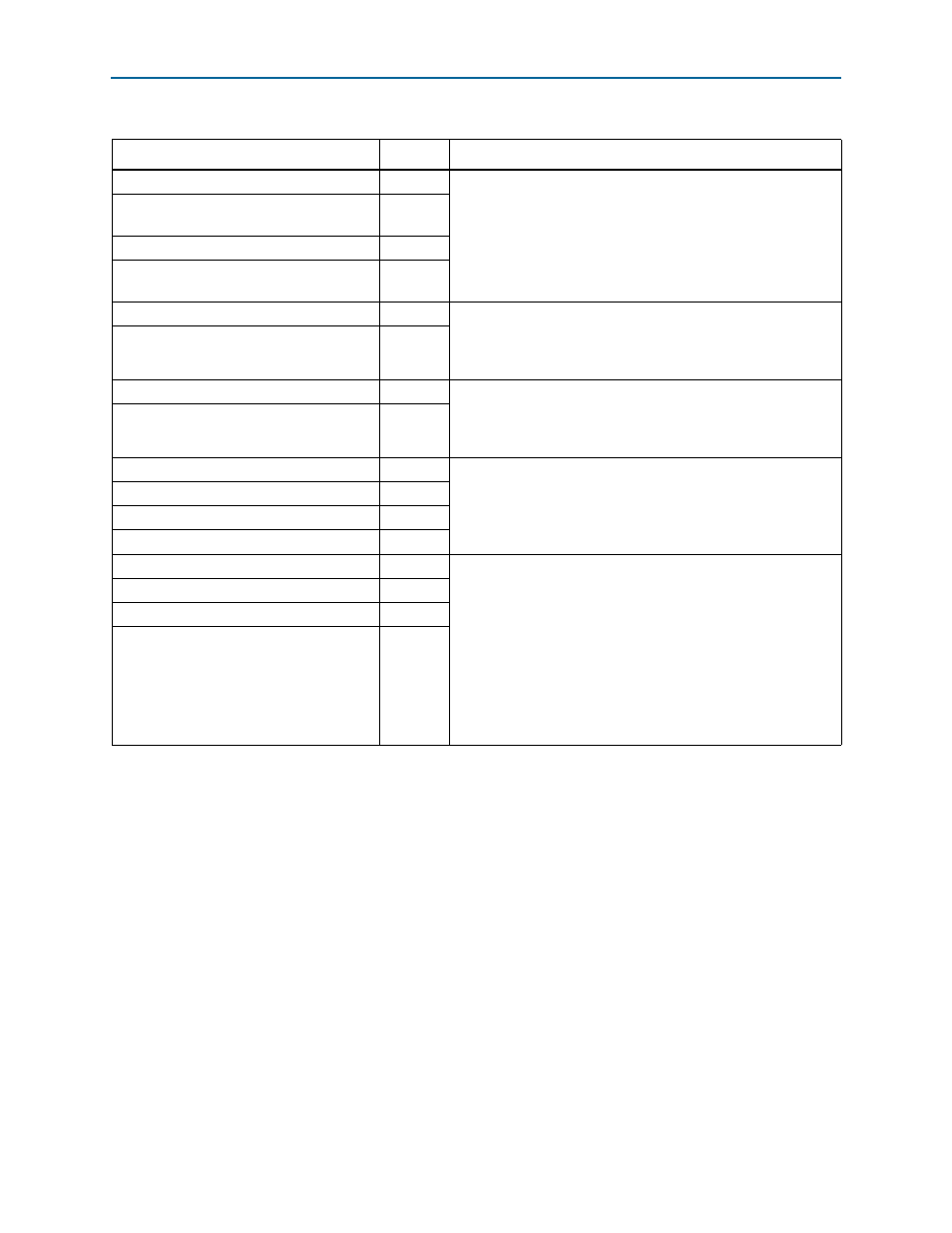

Table 5–15. Capture Signals

Signal

Direction

Description

external_capture_destinationID_wr

Input

Support user logic in setting the corresponding fields in the

Logical/Transport Layer Device ID Capture

CSR at

offset 0x308, For information about the register fields these

signals can write, refer to

external_capture_destinationID_in

[15:0]

Input

external_capture_sourceID_wr

Input

external_capture_sourceID_in

[15:0]

Input

capture_ftype_wr

Input

Support user logic in setting the FTYPE field in the

Logical/Transport Layer Control Capture

CSR at offset

0x308, For information about the register fields these signals can

write, refer to

capture_ftype_in[3:0]

Input

capture_ttype_wr

Input

Support user logic in setting the TTYPE field in the

Logical/Transport Layer Control Capture

CSR at offset

0x308, For information about the register fields these signals can

write, refer to

capture_ttype_in[3:0]

Input

letter_wr

Input

Support user logic in setting bits [3:0] of the MSG_INFO field in

the Logical/Transport Layer Control Capture CSR at

offset 0x308, The two signal pairs write to distinct bits and can be

written simultaneously. For information about the register fields

these signals can write, refer to

letter_in[1:0]

Input

mbox_wr

Input

mbox_in[1:0]

Input

msgseg_wr

Input

Support user logic in setting bits [7:4] of the the MSG_INFO field

in the Logical/Transport Layer Control Capture CSR at

offset 0x308, For information about this register field, refer to

The two signal pairs write to the same register bits. The value of

xmbox_in

is written to MSG_INFO[7:4] only when xmbox_wr

has the value of 1’b1 and msgseg_wr has the value of 1’b0. The

value of msgseg_wr is written to MSG_INFO[7:4]when

msgseg_wr

has the value of 1’b1, irrespective of the value of

xmbox_wr

. ))

msgseg_in[3:0]

Input

xmbox_wr

Input

xmbox_in[3:0]

Input

Note to

:

(1) To write to the register field for any of these signal pairs, drive the value on the _in signal and then set the _wr signal to the value of 1’b1. When

the _wr signal has the value of 1’b1, on the rising edge of sys_clk, the value of the _in signal is written directly to the register field.

(2) To ensure the signals are captured as required by the Error Management Extensions block, you must assert the _wr signal for each of these

signals at the same time you assert the relevant error setting signal from