Csr at offset 0x15c – Altera RapidIO II MegaCore Function User Manual

Page 155

Chapter 6: Software Interface

6–17

Physical Layer Registers

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

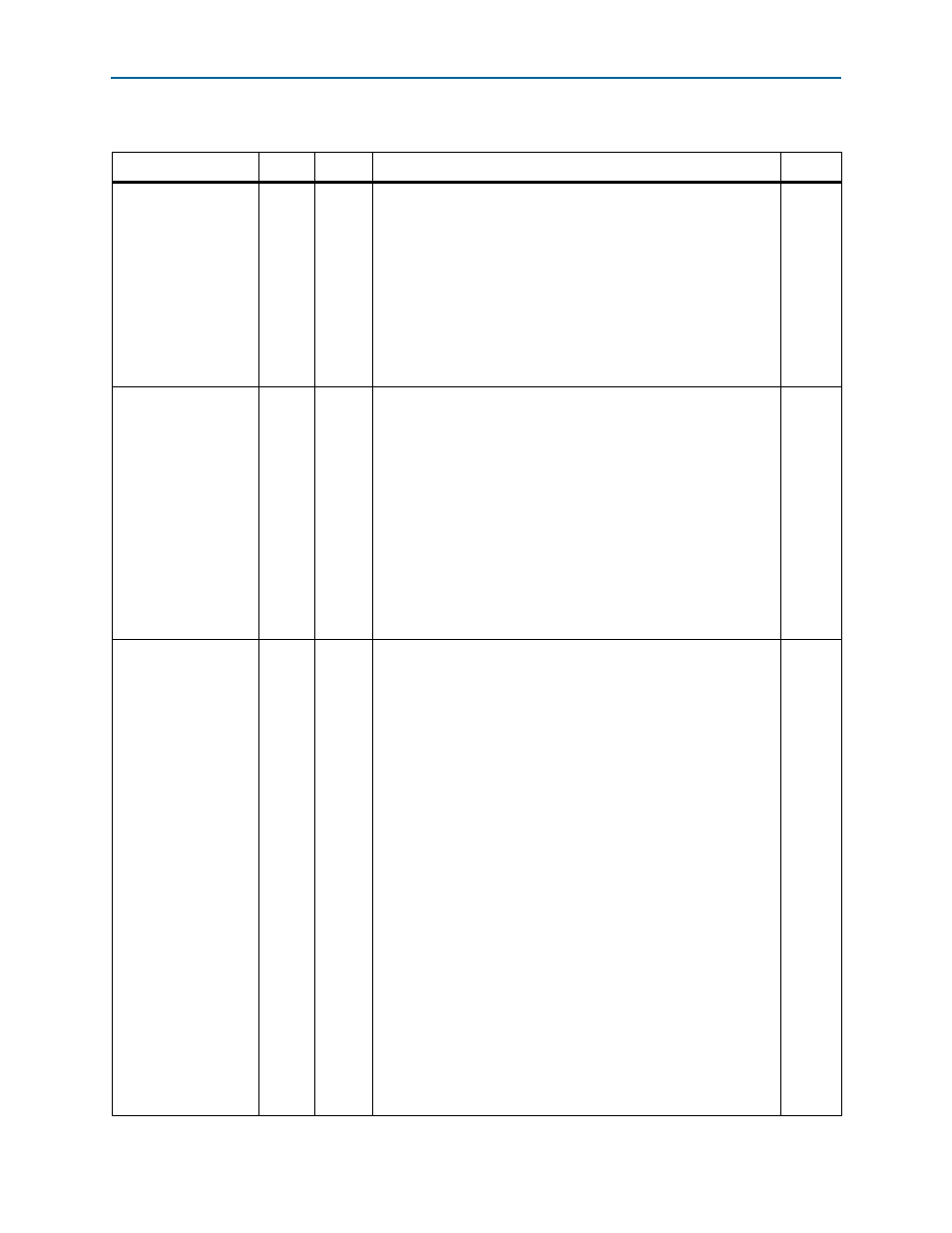

Table 6–15. Port 0 Control CSR—Offset: 0x15C (Part 1 of 4)

Field

Bits

Access

Function

Default

PORT_WIDTH

[31:30] RO

Together with the EXTENDED_PORT_WIDTH field, indicates the

hardware widths this port supports in addition to the 1× (single

lane) width:

Bit [31]: 2× (two-lane) support

1’b0: This port does not support a 2× RapidIO link.

1’b1: This port supports a 2× RapidIO link.

Bit[30]: 4× (four-lane) support

1’b0: This port does not support a 4× RapidIO link.

1’b1: This port supports a 4× RapidIO link.

INIT_WIDTH

[29:27] RO

Width of the port after being initialized:

3'b000: Single lane port, lane 0.

3'b001: Single lane port, lane R (redundancy lane).

3'b010: Four-lane port.

3'b011: Two-lane port.

3’b100: Eight-lane port.

3’b101: Sixteen-lane port.

3’b110–3'b111—Reserved.

This field is reset to the largest supported port width, which can be

any of 3’b000, 3’b010, and 3’b011, based on your selection in the

RapidIO II parameter editor.

PWIDTH_OVRIDE

[26:24] RW

Together with the EXTENDED_PWIDTH_OVRIDE field (bits [15:14]),

indicates soft port configuration to control the width modes

available for port initialization.

■

When bit [26] has the value of 1’b0, bits [15:14] are Reserved.

■

When bit [26] has the value of 1’b1:

■

Bit [25] is the Enable bit for 4× mode.

■

Bit [24] is the Enable bit for 2× mode.

■

Bit [15] is the Enable bit for 8× mode.

■

Bit [14] is the Enable bit for 16× mode.

The RapidIO II IP core supports the following valid values for

{PWIDTH_OVRIDE,EXTENDED_PWIDTH_OVRIDE}:

5'b000xx—All lane widths that the port supports are enabled.

5'b010xx—Force single lane, lane R not forced

5'b011xx—Force single lane, force lane R.

5'b10100—2× mode is enabled, 4× mode is disabled.

5’b11000—4× mode is enabled, 2× mode is disabled.

5'b11100—2× and 4× modes are enabled.

All other values are Reserved.

When the value in the PWIDTH_OVRIDE or

EXTENDED_PWIDTH_OVRIDE

field changes, the port re-initializes

using the new field values.

3'b000