Command and status registers (csrs), Command and status registers (csrs) –32, Command and status registers (csrs)” on – Altera RapidIO II MegaCore Function User Manual

Page 170: Csr at offset 0x48, Table 6–32 on

6–32

Chapter 6: Software Interface

Transport and Logical Layer Registers

RapidIO II MegaCore Function

August 2014

Altera Corporation

User Guide

Command and Status Registers (CSRs)

through

describe the command and status registers.

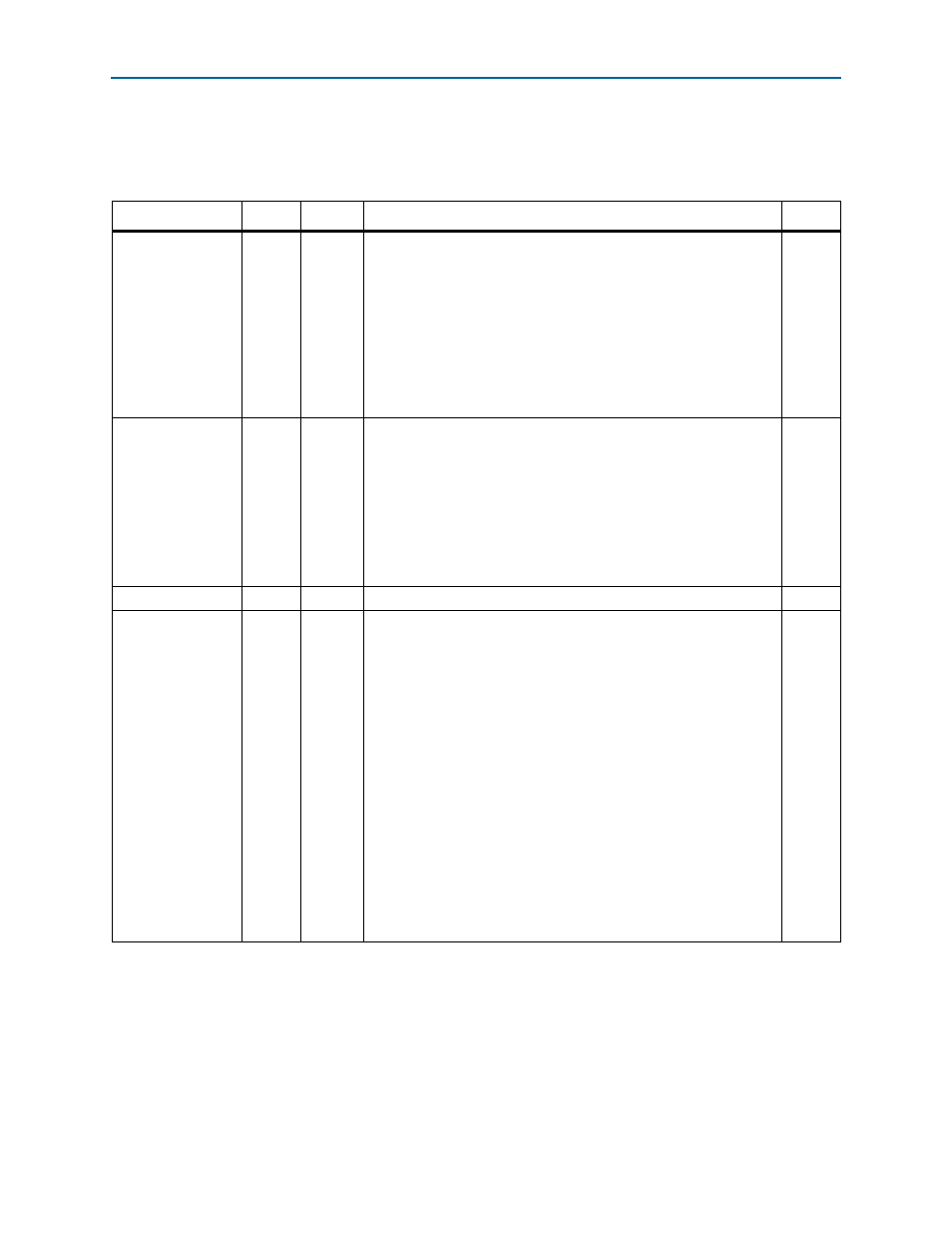

Table 6–32. Data Streaming Logical Layer Control CSR—Offset: 0x48

Field

Bits

Access

Function

Default

TM_TYPE_SUPPORT

[31:28]

RO

TM types supported. This field indicates the TM types that the

RapidIO II IP core variation supports.

The following values are valid:

4'b1000: Supports basic type

4’b1100: Supports basic and rate types

4’b1010: Supports basic and credit types

4’b1110: Supports basic, rate, and credit types

All other values are invalid.

TM_MODE

[27:24]

RW

Traffic management mode. The following values are valid:

4'b0000: TM disabled

4’b0001: Basic mode

4’b0010: Rate mode

4’b0011: Credit mode

4’b0101–4’b0111: Reserved

4’b1000–4’b1111: Available for user-defined modes

RSRV

[23:8]

RO

Reserved

29'h0

[7:0]

RW

Maximum transmission unit. This field controls the data payload size

for segments of an encapsulated PDU. All segments of a PDU except

the final segment must have a data payload of the length specified in

this field. The MTU is a multiple of four bytes.

The following values are valid:

8'b0000_1000: 32-byte block size

8’b0000_1001: 64-byte block size

8’b0000_1010: 40-byte block size

...

8’b0100_0000: 256-byte block size

The following values are invalid:

8’b0000_0000–8’b0000_0111: Reserved

8’b0100_0001–8’b1111_1111: Reserved

Notes to

:

(1) To change the value of this field dynamically during normal operation, use the corresponding _wr and _in signals to control the timing of the

value changes.

(2) The reset value is set in the RapidIO II parameter editor.